保密级别:外部使用

# UM32Mx56 用户手册

版本: V1.0.1

广芯微电子 (广州) 股份有限公司

http://www.unicmicro.com/

UM32Mx56 用户手册 条款协议

## 条款协议

本文档的所有部分,其著作产权归广芯微电子(广州)股份有限公司(以下简称广芯微电子) 所有,未经广芯微电子授权许可,任何个人及组织不得复制、转载、仿制本文档的全部或部分组件。 本文档没有任何形式的担保、立场表达或其他暗示,若有任何因本文档或其中提及的产品所有资讯 所引起的直接或间接损失,广芯微电子及所属员工恕不为其担保任何责任。除此以外,本文档所提 到的产品规格及资讯仅供参考,内容亦会随时更新,恕不另行通知。

- 本文档中所记载的关于电路、软件和其他相关信息仅用于说明半导体产品的操作和应用实例。

用户如在设备设计中应用本文档中的电路、软件和相关信息,请自行负责。对于用户或第三方因使用上述电路、软件或信息而遭受的任何损失,广芯微电子不承担任何责任。

- 在准备本文档所记载的信息的过程中,广芯微电子已尽量做到合理注意,但是,广芯微电子并不保证这些信息都是准确无误的。用户因本文档中所记载的信息的错误或遗漏而遭受的任何损失、广芯微电子不承担任何责任。

- 3. 对于因使用本文档中的广芯微电子产品或技术信息而造成的侵权行为或因此而侵犯第三方的专利、版权或其他知识产权的行为,广芯微电子不承担任何责任。本文档所记载的内容不应视为对广芯微电子或其他人所有的专利、版权或其他知识产权作出任何明示、默示或其它方式的许可及授权。

- 4. 使用本文档中记载的广芯微电子产品时,应在广芯微电子指定的范围内,特别是在最大额定值、电源工作电压范围、热辐射特性、安装条件以及其他产品特性的范围内使用。对于在上述指定范围之外使用广芯微电子产品而产生的故障或损失,广芯微电子不承担任何责任。

- 5. 虽然广芯微电子一直致力于提高广芯微电子产品的质量和可靠性,但是,半导体产品有其自身的具体特性,如一定的故障发生率以及在某些使用条件下会发生故障等。此外,广芯微电子产品均未进行防辐射设计。所以请采取安全保护措施,以避免当广芯微电子产品在发生故障而造成火灾时导致人身事故、伤害或损害的事故。例如进行软硬件安全设计(包括但不限于冗余设计、防火控制以及故障预防等)、适当的老化处理或其他适当的措施等。

# 目录

| 1 | 文档   | 约定    |                                       | 1  |

|---|------|-------|---------------------------------------|----|

|   | 1.1  | 寄存    | 字器相关缩写词列表                             | 1  |

|   | 1.2  | 词氵    | C表                                    | 1  |

| 2 | 产品简介 |       |                                       |    |

|   | 2.1  |       | 充概述                                   |    |

|   | 2.2  | 主要    | 要特性                                   | 3  |

| 3 | 存储   | 器和总   | 总线架构                                  | ć  |

|   | 3.1  |       | 充架构                                   |    |

|   | 3.2  | 总约    | 线架构图                                  | 7  |

|   | 3.3  | 存值    | 诸器映射(Memory Mapping)                  | 8  |

| 4 | 处理   | 2器    |                                       | 10 |

|   | 4.1  |       | 巷                                     |    |

|   | 4.2  |       | 要特性                                   |    |

|   | 4.3  |       | ···<br>能框图                            |    |

|   | 4.4  |       | · · · · · · · · · · · · · · · · · · · |    |

| 5 | 系统   | 置短    | (SCU)                                 | 12 |

|   | 5.1  | 时银    | 中框图                                   | 12 |

|   | 5.2  | 时钟    | 中选择                                   | 12 |

|   | 5.3  | 复信    | 立源                                    | 13 |

|   |      | 5.3.1 | 内部 POR 上电复位                           | 13 |

|   |      | 5.3.2 | LVR 复位                                | 13 |

|   |      | 5.3.3 | RESETEN 复位                            | 13 |

|   |      | 5.3.4 | LOCKUP 复位                             | 14 |

|   |      | 5.3.5 | LVD 复位                                | 14 |

|   |      | 5.3.6 | WDT 复位                                | 14 |

|   |      | 5.3.7 | WWDT 复位                               | 14 |

|   |      | 5.3.8 | SOFT_RESETN 复位                        | 14 |

|   |      | 5.3.9 | 模块复位                                  | 14 |

|   | 5.4  | 低功    | 力耗模式                                  | 14 |

|   |      | 5.4.1 | Sleep 模式                              | 16 |

|   |      | 5.4.2 | DeepSleep 模式                          | 16 |

|   |      | 5.4.3 | Stop 模式                               | 17 |

|   | 5.5  | 系统    | 统寄存器                                  | 18 |

|   |      | 5.5.1 | 系统控制寄存器 0 SCU_CTRL0(偏移: 000h)         | 19 |

|                 | 5.5.2              | 系统控制保护寄存器 SCU_CTRL_PROT(偏移: 008h)           | 20 |

|-----------------|--------------------|---------------------------------------------|----|

|                 | 5.5.3              | 时钟控制寄存器 SCU_OSC_CTRL(偏移: 0x00Ch)            | 20 |

|                 | 5.5.4              | 外围模块时钟寄存器 SCU_PERI_CLKEN(偏移: 010h)          | 20 |

|                 | 5.5.5              | 复位标识寄存器 SCU_RESET_FLAG(偏移: 020h)            | 22 |

|                 | 5.5.6              | 外围模块复位控制寄存器 SCU_PERI_RESET(偏移: 024h)        | 23 |

|                 | 5.5.7              | 外部复位滤波控制寄存器 SCU_EXTRST_CTRL(偏移: 028h)       | 25 |

|                 | 5.5.8              | 端口 PA 功能配置寄存器 SCU_PA_SEL(偏移: 030h)          | 25 |

|                 | 5.5.9              | 端口 PB 功能配置寄存器 SCU_PB_SEL(偏移: 034h)          | 27 |

|                 | 5.5.10             | 端口 PC 功能配置寄存器 SCU_PC_SEL (偏移: 038h)         | 31 |

|                 | 5.5.11             | 端口 PD 功能配置寄存器 SCU_PD_SEL (偏移: 03Ch)         | 33 |

|                 | 5.5.12             | 端口数模配置寄存器 SCU_PAD_ADS(偏移: 054h)             | 35 |

|                 | 5.5.13             | 端口驱动能力配置寄存器 SCU_PAD_DR(偏移: 060h)            | 37 |

|                 | 5.5.14             | 端口上拉配置寄存器 SCU_PAD_PU(偏移: 06Ch)              | 38 |

|                 | 5.5.15             | 端口下拉配置寄存器 SCU_PAD_PD(偏移: 078h)              | 40 |

|                 | 5.5.16             | 端口开漏输出配置寄存器 SCU_PAD_OD(偏移: 084h)            | 41 |

|                 | 5.5.17             | 端口输入类型配置寄存器 SCU_PAD_CS(偏移: 090h)            | 43 |

|                 | 5.5.18             | 端口输入配置寄存器 SCU_PAD_IE(偏移: 09Ch)              | 45 |

|                 | 5.5.19             | 端口输入电平寄存器 SCU_PAD_STATUS (偏移: 0A4h)         | 46 |

|                 | 5.5.20             | 端口速度配置寄存器 SCU_PAD_SR (偏移: 0A8h)             | 48 |

|                 | 5.5.21             | IO 控制保护寄存器 SCU_IOCTRL_PROT(偏移: 0B4h)        | 50 |

|                 | 5.5.22             | LVD 配置寄存器 SCU_LVD_CFG(偏移: 0B8h)             | 50 |

|                 | 5.5.23             | PGA 控制寄存器 SCU_PGA_CFG(偏移: 0BCh)             | 51 |

|                 | 5.5.24             | 外部复位端口选择寄存器 SCU_EXTRST_SEL (偏移: 0D0h)       | 53 |

|                 | 5.5.25             | 停止模式选择寄存器 SCU_STOP_SEL(偏移: 0D4h)            | 54 |

|                 | 5.5.26             | 软件复位寄存器 SCU_SOFT_RSTN (偏移: 0D8h)            |    |

|                 | 5.5.27             | 中断向量地址重映射寄存器 SCU_VET_OFFSET (偏移: 0DCh)      | 54 |

|                 | 5.5.28             | LVD 中断寄存器 SCU_LVD_INTR(偏移: FCh)             | 54 |

|                 | 5.5.29             | VREF 控制寄存器 SCU_VREF(偏移: 188h)               | 55 |

| =FC             |                    |                                             | 56 |

| -ı C<br>6.1     |                    |                                             |    |

| 6.2             |                    |                                             |    |

| 6.3             |                    | n 数据防护机制                                    |    |

| 0.0             | 6.3.1              | eFlash 存储区域                                 |    |

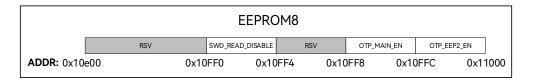

|                 | 6.3.2              | EEPROM 配置字                                  |    |

|                 |                    | SWD 硬件禁止                                    |    |

| 6.4             |                    | 描述                                          |    |

| J. <del>T</del> | 6.4.1              | EFC 控制寄存器(EFC_CTRL)(偏移:00h)                 |    |

|                 |                    | EFC OTP 状态寄存器 (EFC_OTPSTATUS) (偏移: 04h)     |    |

|                 | J. <del>4</del> .Z | LICOIT 7//心可订面 (LIC_OITSIATOS) (M479. U411) | 00 |

|   | 6.4.3  | EFC KEY 输入寄存器(EFC_KEY)(偏移:08h)            | 61 |

|---|--------|-------------------------------------------|----|

|   | 6.4.4  | EFC 中断状态寄存器(EFC_INTSTATUS)(偏移:0Ch)        | 61 |

|   | 6.4.5  | EFC 中断使能寄存器(EFC_INTEN)(偏移:10h)            | 63 |

|   | 6.4.6  | EFC 擦写控制寄存器(EFC_EP_CTRL)(偏移:14h)          | 64 |

|   | 6.4.7  | EFC LDO TRIM 寄存器(EFC_LDOTRIM)(偏移:1Ch)     | 64 |

|   | 6.4.8  | EFC RCH TRIM 寄存器(EFC_RCHTRIM)(偏移: 20h)    | 65 |

|   | 6.4.9  | EFC RCL TRIM 寄存器(EFC_RCLTRIM)(偏移:24h)     | 65 |

|   | 6.4.1  | 0 EFC PGA0 TRIM 寄存器(EFC_PGA0TRIM)(偏移:28h) | 65 |

|   | 6.4.1  | 1 EFC PGA1 TRIM 寄存器(EFC_PGA1TRIM)(偏移:2Ch) | 65 |

|   | 6.4.1  | 2 EFC ADC TRIM 寄存器(EFC_ADCTRIM)(偏移:30h)   | 65 |

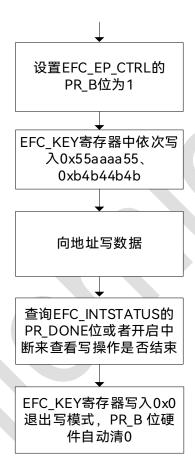

|   | 6.5 软化 | 牛流程                                       | 66 |

|   | 6.5.1  | Write 操作                                  | 66 |

|   | 6.5.2  | Erase 操作                                  | 67 |

| 7 | NIVIC  |                                           | 68 |

| , |        | <b>本</b>                                  |    |

|   |        | 要特性                                       |    |

|   |        | 断源                                        |    |

|   |        |                                           |    |

| 8 |        | <u></u>                                   |    |

|   |        | <u> </u>                                  |    |

|   |        | 要特性                                       |    |

|   |        | 字器描述                                      |    |

|   | 8.3.1  | _ , (ind)                                 |    |

|   |        | 3.3.1.1 GPIO 输出置位寄存器(GPIO_SET)(偏移: 08h)   |    |

|   | 8.3.2  |                                           |    |

|   |        | GPIO 输出引脚映射寄存器(GPIO_ODATA)(偏移: 10h)       |    |

|   | 8.3.4  |                                           |    |

|   | 8.3.5  |                                           |    |

|   | 8.3.6  | GPIO 中断触发模式寄存器(GPIO_IS)(偏移:1Ch)           | 73 |

|   | 8.3.7  | GPIO 中断边沿触发设置寄存器(GPIO_IBE)(偏移:20h)        | 73 |

|   | 8.3.8  | GPIO 中断高低电平触发设置寄存器(GPIO_IEV)(偏移:24h)      | 73 |

|   | 8.3.9  | GPIO 中断状态清除寄存器(GPIO_IC)(偏移:28h)           | 73 |

|   | 8.3.1  | 0 GPIO 原始中断状态寄存器(GPIO_RIS)(偏移:2Ch)        | 74 |

|   | 8.3.1  | 1 GPIO 屏蔽后中断状态寄存器(GPIO_MIS)(偏移:30h)       | 74 |

|   | 8.3.1  | 2 GPIO 输入滤波选择寄存器(GPIO_FLS)(偏移:34h)        | 74 |

|   | 8.4 使原 | <b></b>                                   | 75 |

|   | 8.4.1  | 输入输出 IO                                   | 75 |

|   | 8.4.2  | 中断触发模式                                    | 75 |

|    | 8.4.3   | 清除中断                              | 75 |

|----|---------|-----------------------------------|----|

|    | 8.4.4   | 输入滤波                              | 76 |

| 9  | UART0/1 |                                   | 77 |

|    | 9.1 概述  |                                   | 77 |

|    | 9.2 主要  | 特性                                | 77 |

|    | 9.3 寄存  | 器描述                               | 77 |

|    | 9.3.1   | 中断状态寄存器 UART_ISR(偏移:00h)          | 78 |

|    | 9.3.2   | 中断使能寄存器 UART_IER(偏移:04h)          | 78 |

|    | 9.3.3   | 控制寄存器 UART_CR(偏移:08h)             | 79 |

|    | 9.3.4   | 发送数据寄存器 UART_TDR(偏移:0Ch)          | 80 |

|    | 9.3.5   | 接收数据寄存器 UART_RDR(偏移:10h)          | 80 |

|    | 9.3.6   | 波特率参数低位寄存器 UART_BRR(偏移:14h)       | 80 |

|    | 9.3.7   | 延迟超时寄存器 UART_DLTOR(偏移:18h)        | 80 |

|    | 9.4 使用  | 流程                                | 81 |

|    | 9.4.1   | 串口的发送和接收                          |    |

|    | 9.4.2   | 串口初始化                             | 81 |

|    | 9.4.3   | 串口发送字节                            | 81 |

|    | 9.4.4   | 串口接收字节                            |    |

| 10 | I2C     |                                   | 83 |

|    |         | 述                                 |    |

|    |         | 要特征                               |    |

|    | 10.3 寄  | 存器描述                              | 83 |

|    | 10.3.1  | I2C 主机配置寄存器 I2C_MCFG(偏移: 00h)     | 84 |

|    | 10.3.2  | I2C 主机控制寄存器 I2C_MCON(偏移: 04h)     | 84 |

|    | 10.3.3  | I2C 主机中断使能寄存器 I2C_MIE(偏移: 08h)    | 85 |

|    | 10.3.4  | I2C 主机中断标志寄存器 I2C_MIF(偏移: 0Ch)    | 86 |

|    | 10.3.5  | I2C 主机状态寄存器 I2C_MSTA(偏移: 10h)     | 86 |

|    | 10.3.6  | I2C 主机波特率寄存器 I2C_MBRG(偏移:14h)     | 87 |

|    | 10.3.7  | I2C 主机收发缓存寄存器 I2C_MBUF(偏移:18h)    | 87 |

|    | 10.3.8  | I2C 主机时序控制寄存器 I2C_MTIM(偏移:1Ch)    | 87 |

|    | 10.3.9  | I2C 主机超时寄存器 I2C_MTO(偏移:20h)       | 88 |

|    | 10.3.10 | ) I2C 从机控制寄存器 I2C_SCON(偏移:24h)    | 88 |

|    | 10.3.11 | I I2C 从机中断使能寄存器 I2C_SIE(偏移:28h)   | 89 |

|    | 10.3.12 | 2 I2C 从机中断状态寄存器 I2C_SIF(偏移:2Ch)   | 90 |

|    | 10.3.13 | 3 I2C 从机状态寄存器 I2C_SSTA(偏移:30h)    | 91 |

|    | 10.3.14 | 4 I2C 从机收发缓冲寄存器 I2C_SBUF(偏移:34h)  | 92 |

|    | 10.3.15 | 5 I2C 从机地址寄存器 0 I2C_SADR0(偏移:38h) | 92 |

|    | 10.3.16    | I2C 从机地址寄存器 1 I2C_SADR1(偏移:3Ch)          | 92  |

|----|------------|------------------------------------------|-----|

|    | 10.3.17    | I2C 从机地址寄存器 2 I2C_SADR2(偏移: 40h)         | 92  |

|    | 10.3.18    | I2C 从机地址寄存器 3 I2C_SADR3(偏移: 44h)         | 93  |

|    | 10.4 使用    | ]流程                                      | 94  |

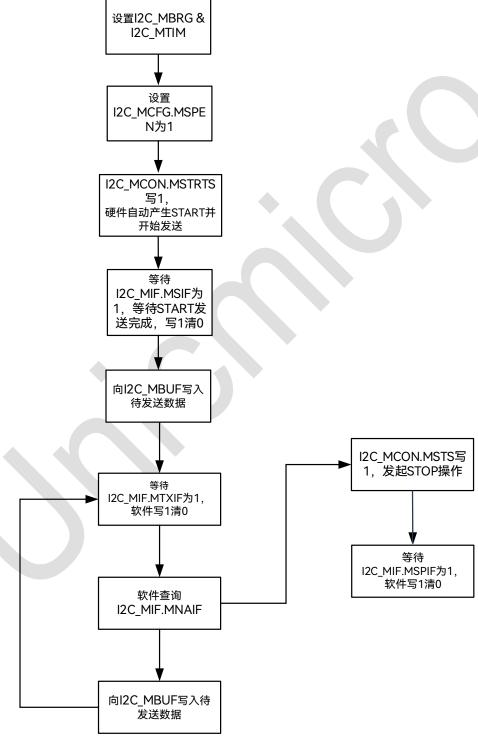

|    | 10.4.1     | 主机发送                                     | 94  |

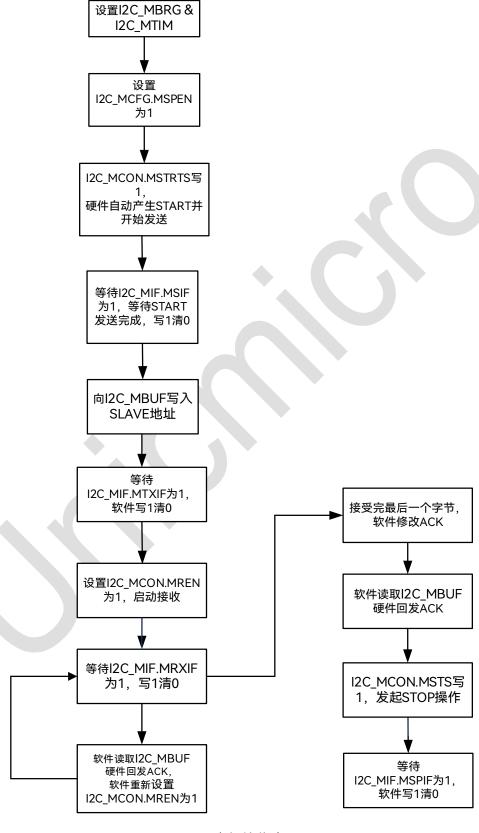

|    | 10.4.2     | 主机接收                                     | 95  |

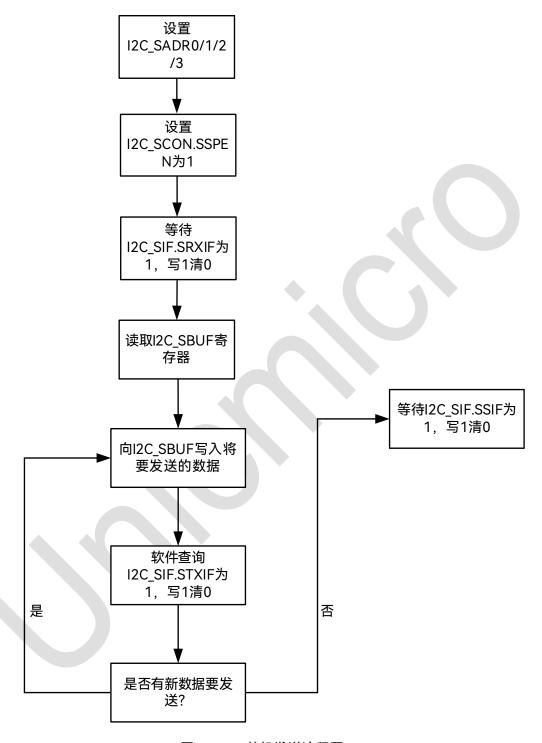

|    | 10.4.3     | 从机发送                                     | 96  |

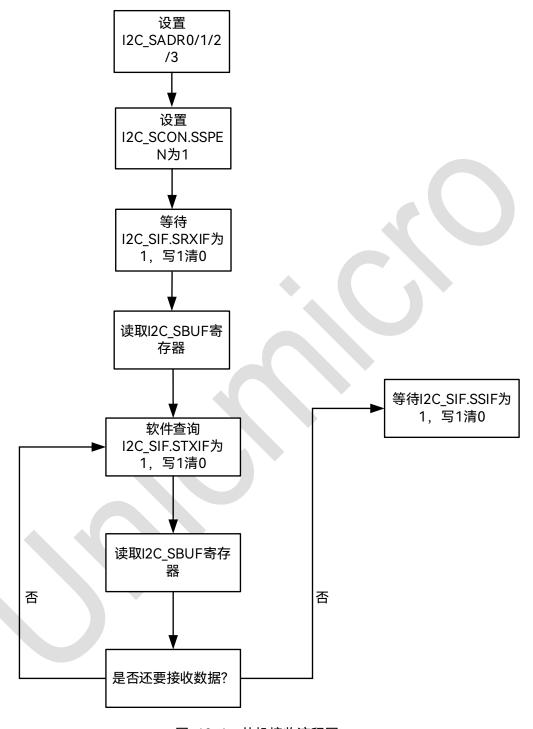

|    | 10.4.4     | 从机接收                                     | 97  |

| 11 | SPI        |                                          | 98  |

|    | 11.1 概划    | <u> </u>                                 | 98  |

|    | 11.2 主要    | <b>長特性</b>                               | 98  |

|    | 11.3 寄存    | 7器描述                                     | 99  |

|    | 11.3.1     | SPI 配置寄存器 (SPI_CR) (偏移: 00h)             | 99  |

|    | 11.3.2     | SPI 主模式控制寄存器 0 (SPI_CS0) (偏移: 04h)       | 101 |

|    | 11.3.3     | SPI 主模式控制寄存器 1(SPI_CS1)(偏移: 08h)         | 102 |

|    | 11.3.4     | SPI 过程控制寄存器(SPI_OPCR)(偏移: 14h)           | 103 |

|    | 11.3.5     | SPI 中断控制寄存器 (SPI_IE) (偏移: 18h)           | 104 |

|    | 11.3.6     | SPI 中断标志寄存器 (SPI_IF) (偏移: 1Ch)           | 105 |

|    | 11.3.7     | SPI 发送缓存寄存器 (SPI_TXBUF) (偏移: 20h)        | 106 |

|    | 11.3.8     | SPI 接收缓存寄存器 (SPI_RXBUF) (偏移: 24h)        | 106 |

|    | 11.3.9     | SPI DMA 接收设置寄存器(SPI_DMARXLEV)(偏移: 28h)   | 106 |

|    | 11.3.10    | SPI DMA 发送设置寄存器 (SPI_DMATXLEV) (偏移: 2Ch) | 106 |

|    | 11.4 使用    | ]流程                                      | 107 |

|    | 11.4.1     | 初始化程序                                    | 107 |

|    | 11.4.2     | 发送流程                                     | 108 |

|    | 11.4.3     | 接收流程                                     | 108 |

|    | 11.4.4     | SPI DMA 发送流程                             | 108 |

|    | 11.4.5     | SPI DMA 接收流程                             | 109 |

| 12 | ATIMER     |                                          | 110 |

|    | 12.1 概划    | <u> </u>                                 | 110 |

|    | 12.2 主要    | 長特性                                      | 110 |

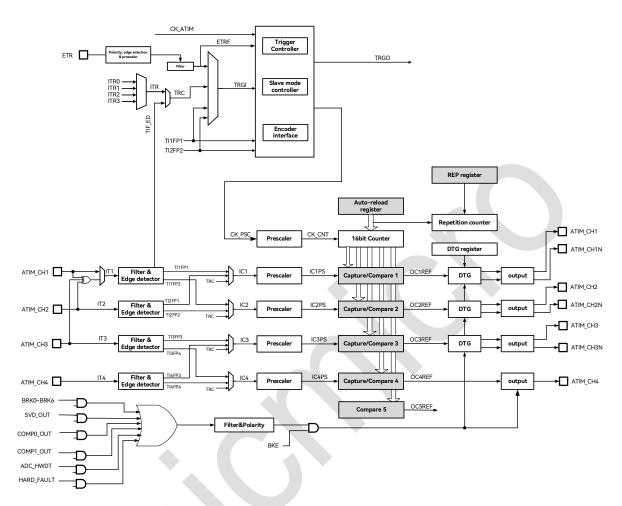

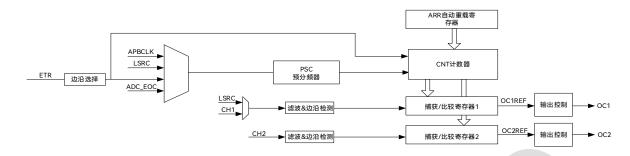

|    | 12.3 ATIME | ER 结构框图                                  | 111 |

|    | 12.4 功能    | b描述                                      | 111 |

|    | 12.4.1     | 定时单元                                     | 111 |

|    | 12.4.2     | 定时器工作模式                                  | 113 |

|    | 12.4.3     | 向上计数                                     | 113 |

|    | 12.4.4     | 向下计数                                     | 116 |

| 12.4.5  | 中心对齐计数                                    | 118 |

|---------|-------------------------------------------|-----|

| 12.4.6  | 重复计数器                                     | 120 |

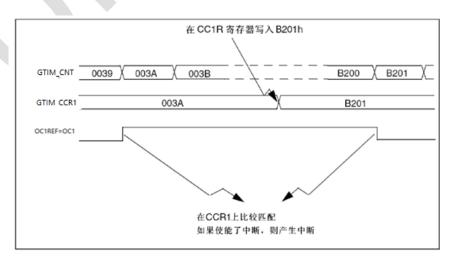

| 12.4.7  | Preload 寄存器                               | 121 |

| 12.4.8  | 计数器工作时钟                                   | 122 |

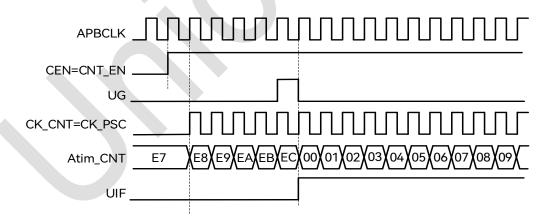

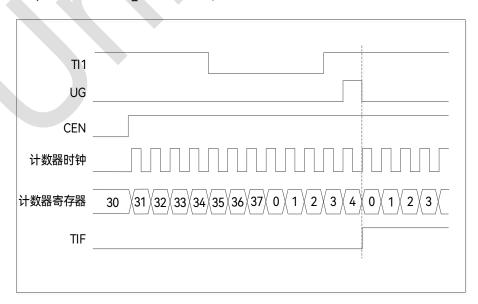

| 12.4.9  | 内部时钟模式                                    | 122 |

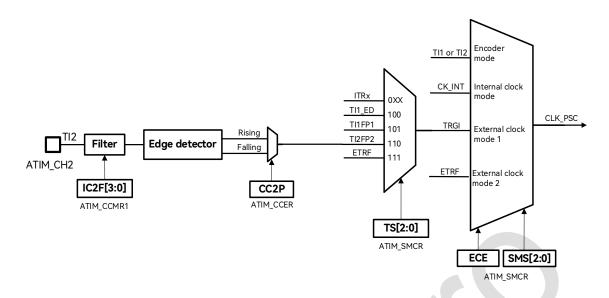

| 12.4.10 | 外部时钟模式 1                                  | 122 |

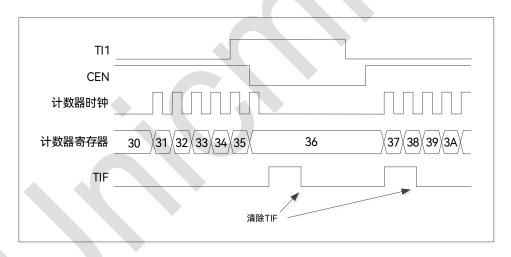

| 12.4.11 | 外部时钟模式 2                                  | 124 |

| 12.4.12 | 内部触发信号(ITRx)                              | 126 |

| 12.4.13 | 捕捉/比较通道                                   |     |

| 12.4.14 | 输入捕捉模式                                    | 128 |

| 12.4.15 | 软件 Force 输出                               | 130 |

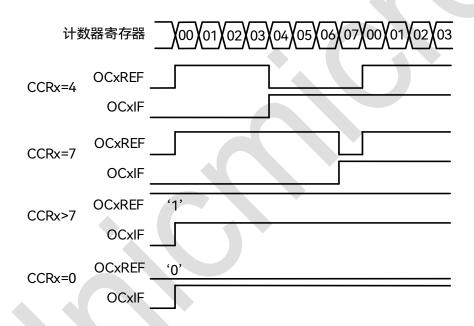

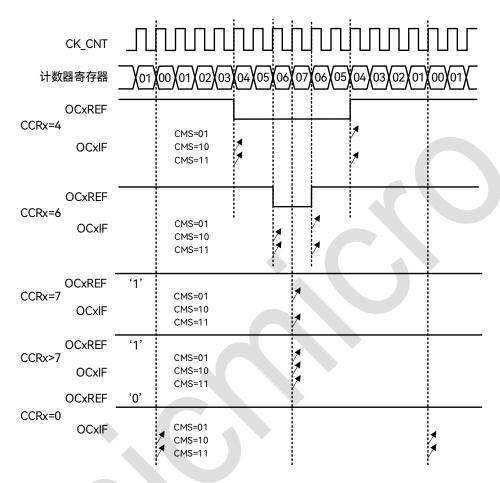

| 12.4.16 | 输出比较模式                                    | 130 |

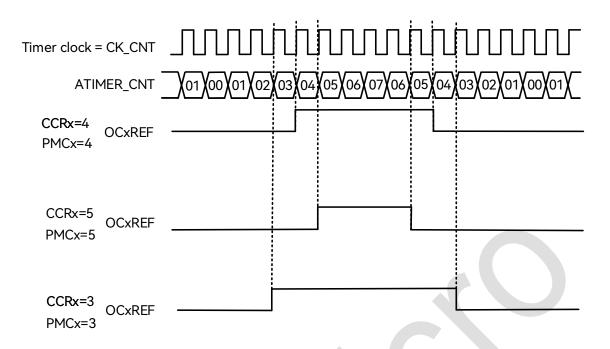

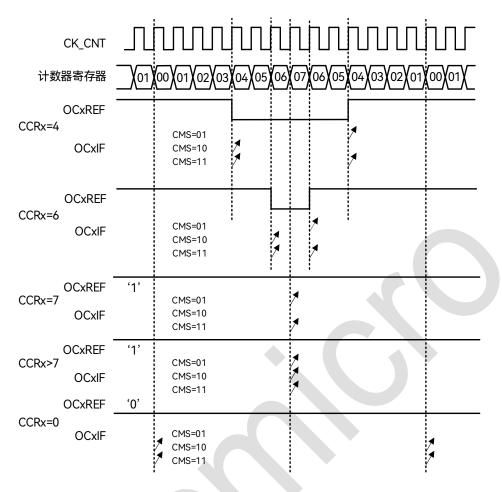

| 12.4.17 | PWM 输出                                    | 131 |

| 12.4.18 | 非对称 PWM 移相控制                              | 133 |

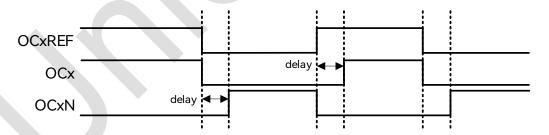

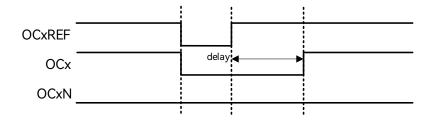

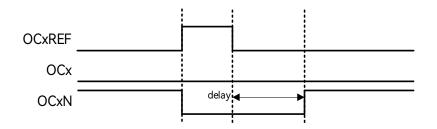

| 12.4.19 | 互补输出和死区插入                                 | 134 |

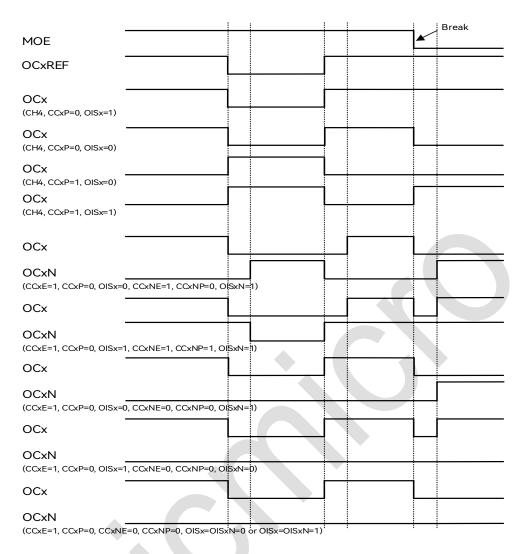

| 12.4.20 |                                           |     |

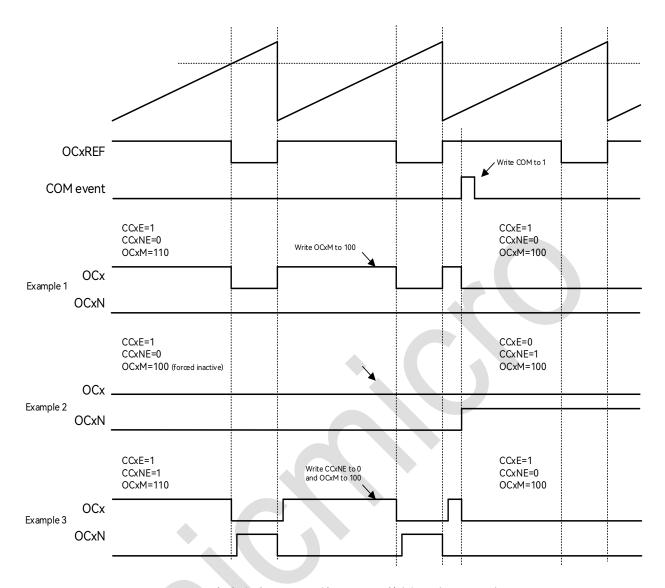

| 12.4.21 | 6-step PWM 输出                             | 136 |

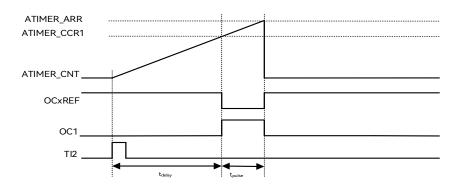

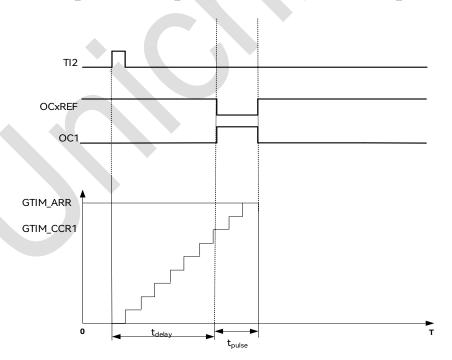

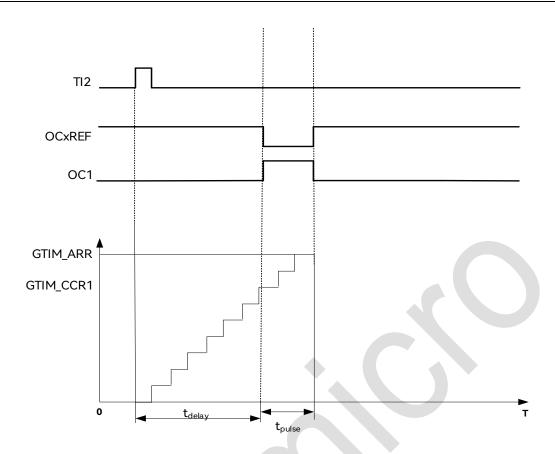

| 12.4.22 | 单脉冲输出                                     | 137 |

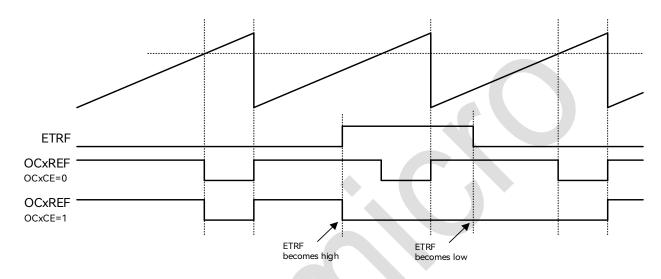

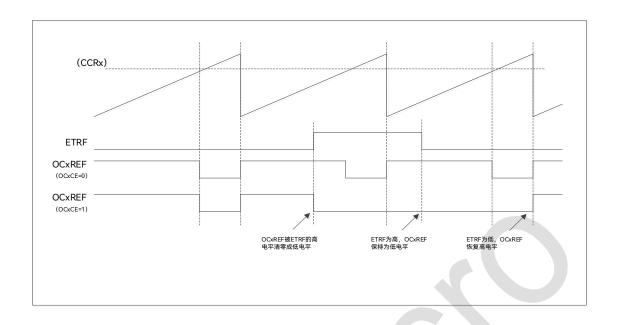

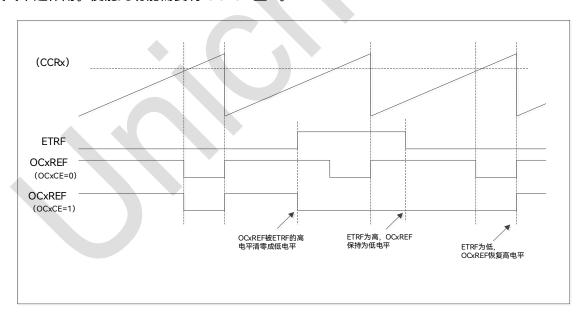

| 12.4.23 | 外部事件清除 OCxREF                             | 139 |

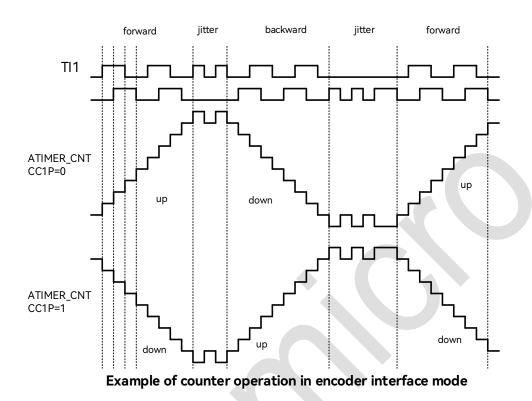

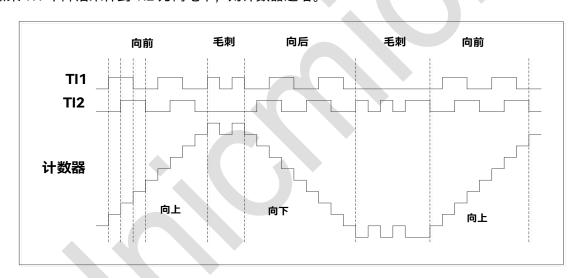

| 12.4.24 | 编码器接口模式                                   | 139 |

| 12.4.25 | ATIMER 从机模式                               | 140 |

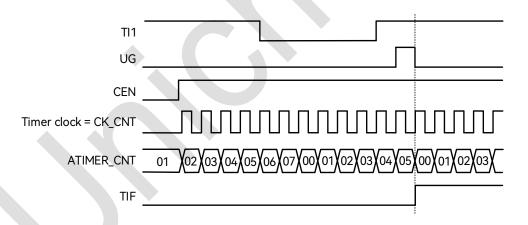

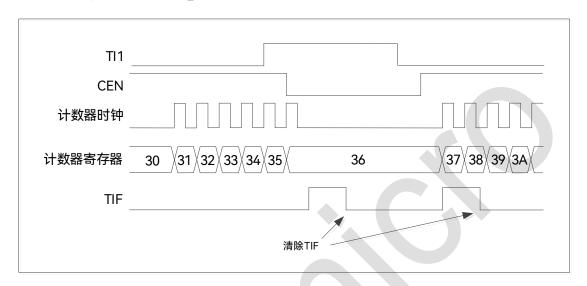

| 12.4.26 | 复位模式                                      | 141 |

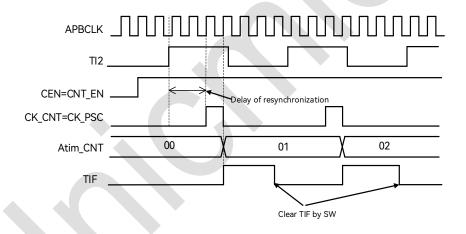

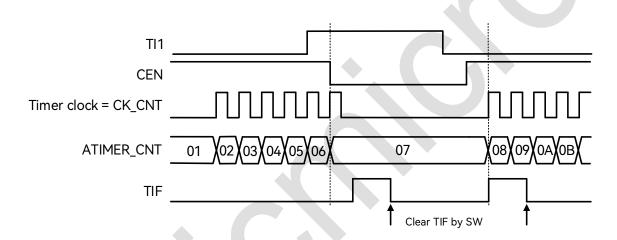

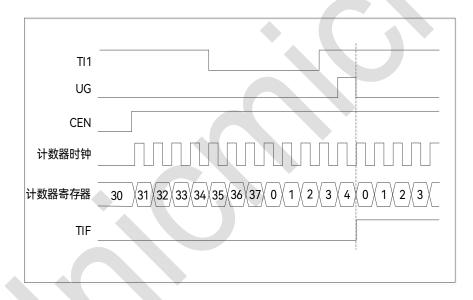

| 12.4.27 | 门控模式                                      | 141 |

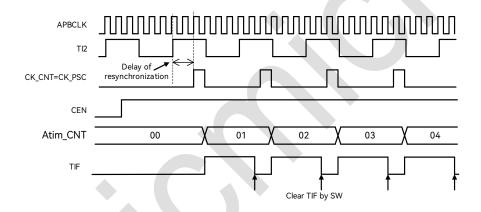

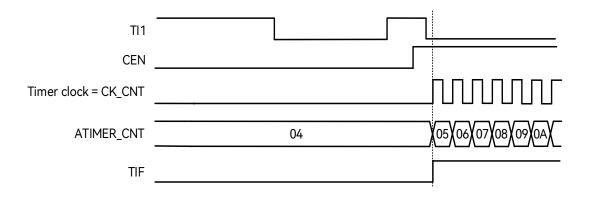

| 12.4.28 | 触发模式                                      | 142 |

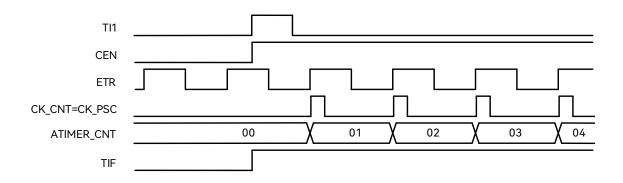

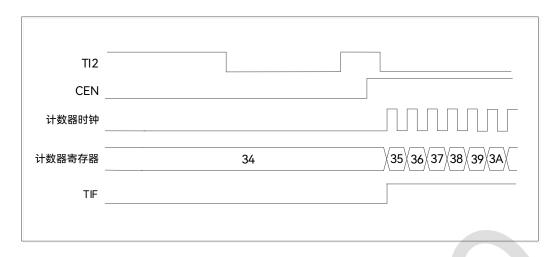

| 12.4.29 | 外部事件触发的外部时钟计数模式                           | 143 |

| 12.4.30 | DMA 访问                                    | 144 |

| 12.4.31 | 输入异或功能                                    | 145 |

| 12.4.32 | Debug 模式                                  | 145 |

| 12.4.33 | DMA Burst                                 | 145 |

| 12.5 寄存 | 字器描述                                      | 146 |

| 12.5.1  | ATIMER 控制寄存器 1 ATIMER_CR1(偏移:00h)         | 147 |

| 12.5.2  | ATIMER 控制寄存器 2 ATIMER_CR2(偏移:04h)         | 149 |

| 12.5.3  | ATIMER 从机模式控制寄存器 ATIMER_SMCR(偏移:08h)      | 151 |

| 12.5.4  | ATIMER DMA 和中断使能寄存器 ATIMER_DIER(偏移:0Ch)   | 152 |

| 12.5.5  | ATIMER 状态寄存器 ATIMER_SR(偏移:10h)            | 154 |

| 12.5.6  | ATIMER 事件产生寄存器 ATIMER_EGR(偏移:14h)         | 155 |

| 12.5.7  | ATIMER 捕捉/比较模式寄存器 1 ATIMER_CCMR1(偏移:18h)  | 156 |

| 12.5.8  | ATIMER 捕捉/比较模式寄存器 2 ATIMER_CCMR2(偏移: 1Ch) | 158 |

|    | 12.5.9  | ATIMER 捕捉/比较使能寄存器 ATIMER_CCER(偏移: 20h)   | 161 |

|----|---------|------------------------------------------|-----|

|    | 12.5.10 | ATIMER 计数器寄存器 ATIMER_CNT(偏移:24h)         | 163 |

|    | 12.5.11 | ATIMER 预分频寄存器 ATIMER_PSC(偏移:28h)         | 164 |

|    | 12.5.12 | ATIMER 自动重载寄存器 ATIMER_ARR(偏移:2Ch)        | 164 |

|    | 12.5.13 | ATIMER 重复计数寄存器 ATIMER_RCR(偏移:30h)        | 164 |

|    | 12.5.14 | ATIMER 捕捉/比较寄存器 1 ATIMER_CCR1(偏移:34h)    | 164 |

|    | 12.5.15 | ATIMER 捕捉/比较寄存器 2 ATIMER_CCR2(偏移:38h)    | 165 |

|    | 12.5.16 | ATIMER 捕捉/比较寄存器 3 ATIMER_CCR3(偏移:3Ch)    | 165 |

|    | 12.5.17 | ATIMER 捕捉/比较寄存器 4 ATIMER_CCR4(偏移:40h)    | 165 |

|    | 12.5.18 | ATIMER 刹车和死区控制寄存器 ATIMER_BDTR(偏移:44h)    | 166 |

|    | 12.5.19 | ATIMER DMA 控制寄存器 ATIMER_DCR(偏移:48h)      | 167 |

|    | 12.5.20 | ATIMER DMA 访问寄存器 ATIMER_DMAR(偏移:4Ch)     | 168 |

|    | 12.5.21 | ATIMER 捕捉/比较模式寄存器 3 ATIMER_CCMR3(偏移:50h) | 168 |

|    | 12.5.22 | ATIMER 捕捉/比较寄存器 5 ATIMER_CCR5(偏移: 54h)   | 169 |

|    | 12.5.23 | ATIMER PWM 移相使能寄存器 ATIMER_PMEN(偏移:58h)   | 169 |

|    | 12.5.24 | ATIMER 移相偏移寄存器 1 ATIMER_PMC1(偏移:5Ch)     | 170 |

|    | 12.5.25 | ATIMER 移相偏移寄存器 2 ATIMER_PMC2(偏移: 60h)    | 170 |

|    | 12.5.26 | ATIMER 移相偏移寄存器 3 ATIMER_PMC3(偏移: 64h)    | 170 |

|    | 12.5.27 | ATIMER 刹车输入控制寄存器 ATIMER_BKCTL(偏移:68h)    | 170 |

|    | 12.6 使用 | 月流程                                      | 172 |

|    | 12.6.1  | 定时计数模式                                   | 172 |

|    | 12.6.2  | PWM 模式                                   | 172 |

|    | 12.6.3  | 输入捕捉模式                                   | 173 |

|    | 12.6.4  | 互补输出和死区插入                                | 174 |

|    | 12.6.5  | 刹车功能                                     | 174 |

|    | 12.6.6  | 编码器接口模式                                  | 175 |

|    | 12.6.7  | DMA 模式                                   | 175 |

| 13 | 通用定时器   | ₹ GTIMER0                                | 177 |

|    | 13.1 概2 | <u>t</u>                                 | 177 |

|    | 13.2 主要 | ē特性                                      | 177 |

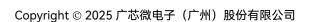

|    | 13.3 通用 | 月定时器 GTIMER0 结构框图                        | 178 |

|    | 13.4 功能 | <b>E描述</b>                               | 178 |

|    | 13.4.1  | 定时单元                                     | 178 |

|    | 13.4.2  | 定时器工作模式                                  | 179 |

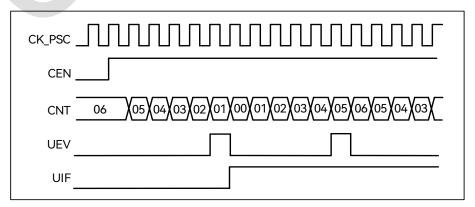

|    | 13.4    | 4.2.1 向上计数                               | 179 |

|    | 13.4    | 4.2.2 向下计数                               | 180 |

|    | 13.4    | 4.2.3 中心对齐计数                             | 181 |

|    | 13.4.3  | 计数器工作时钟                                  | 182 |

|    |         |                                          |     |

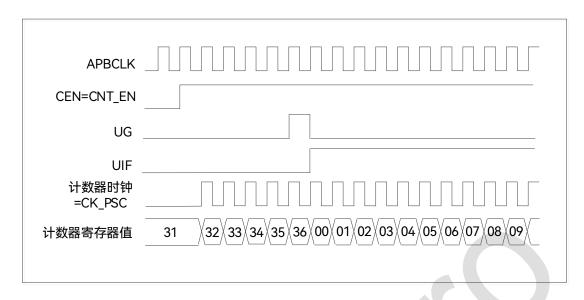

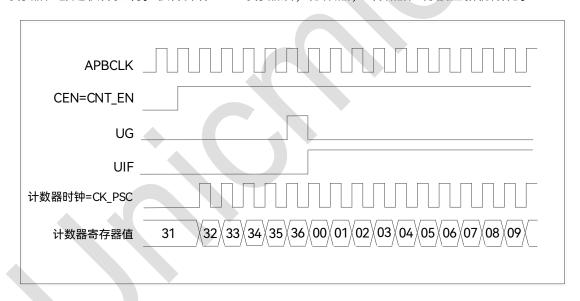

| 13.4    | .3.1 APBCLK                          | 182 |

|---------|--------------------------------------|-----|

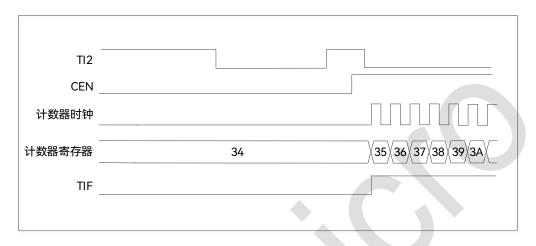

| 13.4    | .3.2 GTIMER_CHx(x=1,2)引脚输入——外部时钟模式 1 | 183 |

| 13.4    | .3.3 GTIMER_ETR 引脚输入——外部时钟模式 2       | 183 |

| 13.4.4  | 内部触发信号(ITRx)                         | 184 |

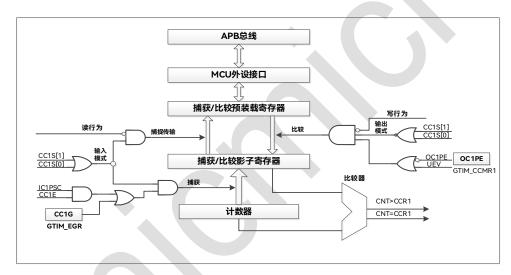

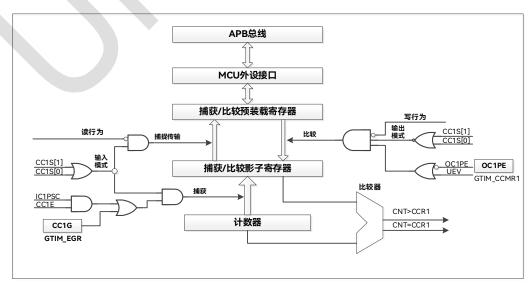

| 13.4.5  | 捕捉/比较通道                              | 184 |

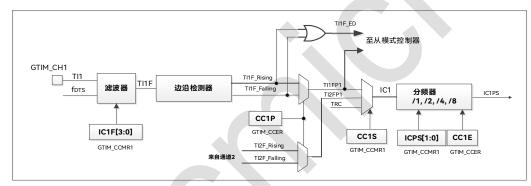

| 13.4    | .5.1 捕获通道                            | 184 |

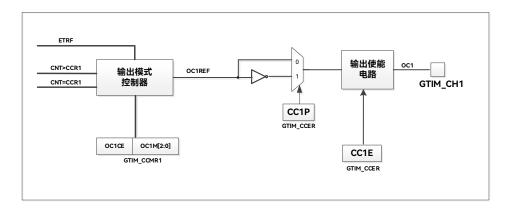

| 13.4    | .5.2 比较通道                            | 185 |

| 13.4.6  | 输入捕捉模式                               | 186 |

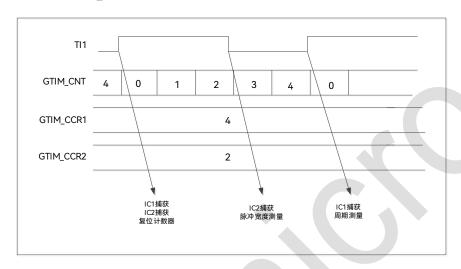

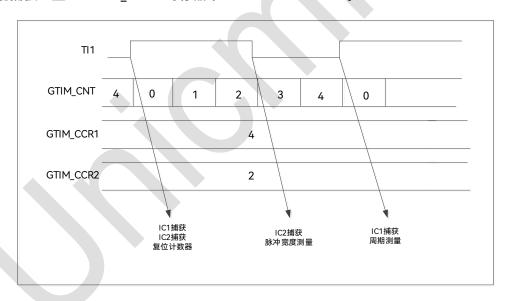

| 13.4.7  | PWM 输入模式                             | 186 |

| 13.4.8  | 软件强制输出                               | 187 |

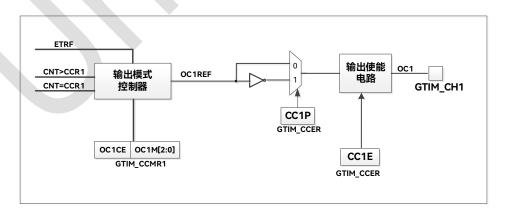

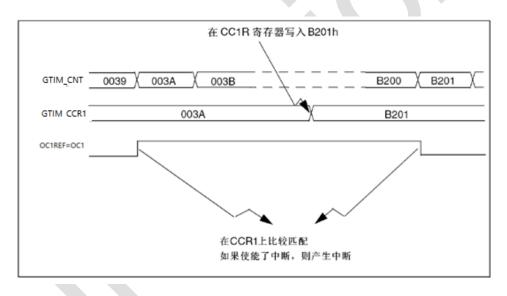

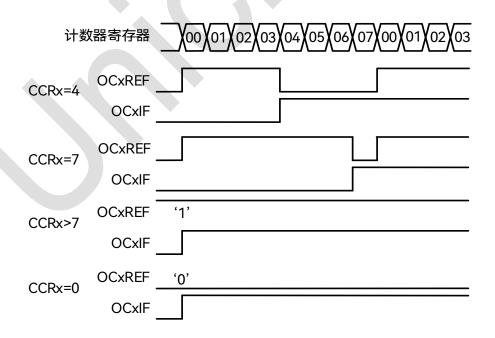

| 13.4.9  | 输出比较模式                               | 187 |

|         | PWM 输出                               |     |

|         | .10.1 PWM 边缘对齐模式                     |     |

| 13.4    | .10.2 PWM 中央对齐模式                     |     |

| 13.4.11 | 输出比较快速使能模式                           | 190 |

| 13.4.12 | 单脉冲输出                                | 191 |

| 13.4.13 | 外部事件清除 OCxREF                        | 192 |

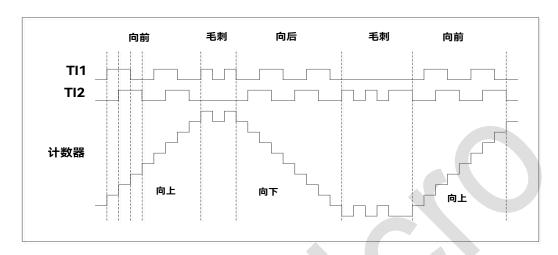

| 13.4.14 | 编码器接口模式(Encoder Interface)           | 193 |

| 13.4.15 | GTIMER 从机模式                          | 194 |

| 13.4    | .15.1 复位模式                           | 194 |

| 13.4    | .15.2 门控模式                           | 195 |

| 13.4    | .15.3 触发模式                           | 196 |

| 13.4.16 | 定时器同步                                | 197 |

| 13.4.17 | DMA Burst                            | 197 |

| 13.4.18 | 输入异或功能                               | 198 |

| 13.4.19 | Debug 模式                             | 198 |

| 3.5 寄存  | 器描述                                  | 198 |

| 13.5.1  | GTIMER 寄存器分布                         | 198 |

| 13.5.2  | 控制寄存器 1 GTIMER_CR1(偏移: 00h)          | 199 |

| 13.5.3  | 控制寄存器 2 GTIMER_CR2(偏移: 04h)          | 200 |

| 13.5.4  | 从机模式控制寄存器 GTIMER_SMCR(偏移: 08h)       | 201 |

| 13.5.5  | DMA 和中断使能寄存器 GTIMER_DIER(偏移: 0Ch)    | 203 |

| 13.5.6  | 状态寄存器 GTIMER_SR(偏移:10h)              | 205 |

| 13.5.7  | 事件产生寄存器 GTIMER_EGR(偏移:14h)           | 206 |

| 13.5.8  | 捕捉/比较模式寄存器 1 GTIMER_CCMR1(偏移: 18h)   | 206 |

|         |                                      |     |

| 13.5.10 |                                      |     |

| 13.5.11 |                                      |     |

|         |                                      |     |

| 13.5.12 预分频寄存器 GTIMER_PSC(偏移:28h)        | 213 |

|------------------------------------------|-----|

| 13.5.13 自动重载寄存器 GTIMER_ARR(偏移:2Ch)       | 213 |

| 13.5.14 捕捉/比较寄存器 1 GTIMER_CCR1(偏移:34h)   | 213 |

| 13.5.15 捕捉/比较寄存器 2 GTIMER_CCR2(偏移:38h)   | 214 |

| 13.5.16 捕捉/比较寄存器 3 GTIMER_CCR3(偏移:3Ch)   | 214 |

| 13.5.17 捕捉/比较寄存器 4 GTIMER_CCR4(偏移:40h)   | 214 |

| 13.5.18 DMA 控制寄存器 GTIMER_DCR(偏移:48h)     | 215 |

| 13.5.19 DMA 访问寄存器 GTIMER_DMAR(偏移:4Ch)    | 215 |

| 14   通用定时器 GTIMER1/2                     | 216 |

| 14.1 概述                                  | 216 |

| 14.2  主要特性                               | 216 |

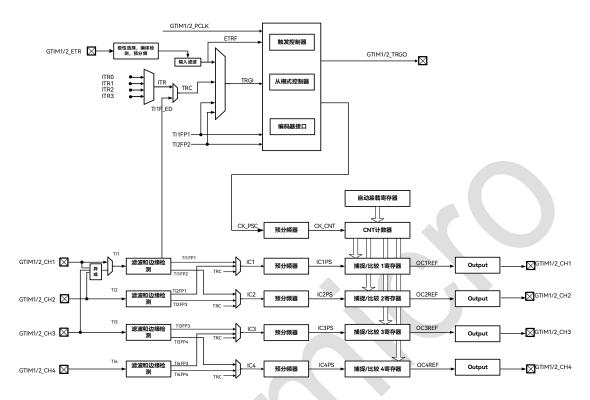

| 14.3  通用定时器 GTIMER1/2 结构框图               | 217 |

| 14.4  功能描述                               | 217 |

| 14.4.1 定时单元                              | 217 |

| 14.4.2 定时器工作模式                           |     |

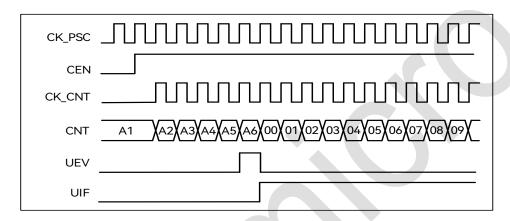

| 14.4.2.1 向上计数                            | 218 |

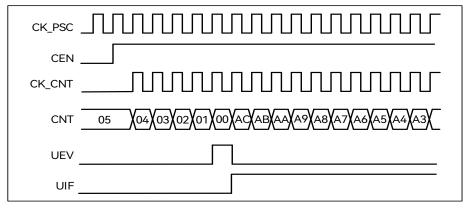

| 14.4.2.2 向下计数                            | 219 |

| 14.4.2.3 中心对齐计数                          | 220 |

| 14.4.3 计数器工作时钟                           |     |

| 14.4.3.1 APBCLK                          | 221 |

| 14.4.3.2 GTIMER_CHx(x=1,2)引脚输入——外部时钟模式 1 | 221 |

| 14.4.3.3 GTIMER_ETR 引脚输入——外部时钟模式 2       | 222 |

| 14.4.4 内部触发信号(ITRx)                      | 222 |

| 14.4.5  捕捉/比较通道                          | 223 |

| 14.4.5.1 捕获通道                            | 223 |

| 14.4.5.2 比较通道                            | 223 |

| 14.4.6 输入捕捉模式                            | 224 |

| 14.4.7 PWM 输入模式                          | 225 |

| 14.4.8 软件强制输出                            | 225 |

| 14.4.9 输出比较模式                            | 226 |

| 14.4.10 PWM 输出                           | 227 |

| 14.4.10.1 PWM 边缘对齐模式                     | 227 |

| 14.4.10.2 PWM 中央对齐模式                     | 228 |

| 14.4.11 输出比较快速使能模式                       | 228 |

| 14.4.12 单脉冲输出                            | 229 |

| 14.4.13 外部事件清除 OCxREF                    | 231 |

| 14.4.14 编码器接口模式(Encoder Interface)       | 231 |

| 14.4.15 GTIMER 从机模式                      | 233 |

|    | 14.4    | 4.15.1 复位模式                        | 233 |

|----|---------|------------------------------------|-----|

|    | 14.4    | 4.15.2 门控模式                        | 234 |

|    | 14.4    | 4.15.3 触发模式                        | 234 |

|    | 14.4.16 | 定时器同步                              | 235 |

|    | 14.4.17 | DMA Burst                          | 235 |

|    | 14.4.18 | 输入异或功能                             | 236 |

|    | 14.4.19 | Debug 模式                           | 236 |

|    | 14.5 寄存 | <b>7</b> 器描述                       | 236 |

|    | 14.5.1  | GTIMER 寄存器分布                       | 236 |

|    | 14.5.2  | 控制寄存器 1 GTIMER_CR1(偏移: 00h)        |     |

|    | 14.5.3  | 控制寄存器 2 GTIMER_CR2(偏移: 04h)        | 239 |

|    | 14.5.4  | 从机模式控制寄存器 GTIMER_SMCR(偏移:08h)      |     |

|    | 14.5.5  | DMA 和中断使能寄存器 GTIMER_DIER(偏移:0Ch)   | 241 |

|    | 14.5.6  | 状态寄存器 GTIMER_SR(偏移:10h)            |     |

|    | 14.5.7  | 事件产生寄存器 GTIMER_EGR(偏移:14h)         | 244 |

|    | 14.5.8  | 捕捉/比较模式寄存器 1 GTIMER_CCMR1(偏移: 18h) | 245 |

|    | 14.5.9  | 捕捉/比较模式寄存器 2 GTIMER_CCMR2(偏移: 1Ch) | 247 |

|    | 14.5.10 | 捕捉/比较使能寄存器 GTIMER_CCER(偏移:20h)     | 250 |

|    | 14.5.11 | 计数器寄存器 GTIMER_CNT(偏移:24h)          | 251 |

|    | 14.5.12 | 预分频寄存器 GTIMER_PSC(偏移:28h)          | 251 |

|    | 14.5.13 | 自动重载寄存器 GTIMER_ARR(偏移: 2Ch)        | 251 |

|    | 14.5.14 | 捕捉/比较寄存器 1 GTIMER_CCR1(偏移:34h)     | 252 |

|    | 14.5.15 | 捕捉/比较寄存器 2 GTIMER_CCR2(偏移:38h)     | 252 |

|    | 14.5.16 | 捕捉/比较寄存器 3 GTIMER_CCR3(偏移:3Ch)     | 252 |

|    | 14.5.17 | 捕捉/比较寄存器 4 GTIMER_CCR4(偏移: 40h)    | 253 |

|    | 14.5.18 | DMA 控制寄存器 GTIMER_DCR(偏移: 48h)      | 253 |

|    | 14.5.19 | DMA 访问寄存器 GTIMER_DMAR(偏移:4Ch)      | 254 |

| 15 | LPTIMER |                                    | 255 |

|    |         | ₹                                  |     |

|    | 15.2 主要 | 夏特性                                | 255 |

|    | 15.3 结构 | 9框图                                | 256 |

|    |         | 寸器功能                               |     |

|    | 15.4.1  | 单次计数和连续计数                          | 256 |

|    | 15.4.2  | ETR 触发计数                           | 256 |

|    | 15.4.3  | ETR 脉冲计数                           | 257 |

|    | 15.4.4  | Timeout 模式                         | 257 |

|    |         | 足比较功能                              |     |

|    | 15.5.1  | PWM 输出                             | 257 |

|    | 15.5.2  | 输入捕捉                                            | 258     |

|----|---------|-------------------------------------------------|---------|

|    | 15.5.3  | Debug 模式                                        | 258     |

|    | 15.6 寄花 | 字器描述                                            | 258     |

|    | 15.6.1  | LPTIMER 控制寄存器 1 LPTIMER_CR1(偏移:00h)             | 258     |

|    | 15.6.2  | LPTIMER 控制寄存器 2 LPTIMER_CR2(偏移: 04h)            | 259     |

|    | 15.6.3  | LPTIMER 中断使能寄存器 LPTIMER_IER(偏移:08h)             | 260     |

|    | 15.6.4  | LPTIMER 中断标志寄存器 LPTIMER_SR(偏移:0Ch)              | 261     |

|    | 15.6.5  | LPTIMER 计数值寄存器 LPTIMER_CNT(偏移:10h)              | 261     |

|    | 15.6.6  | LPTIMER 捕捉比较配置寄存器 1 LPTIMER_CCMCFG1(偏移: 14h)    | 261     |

|    | 15.6.7  | LPTIMER 捕捉比较配置寄存器 2 LPTIMER_CCMCFG2(偏移: 18h)    | 262     |

|    | 15.6.8  | LPTIMER 自动重载寄存器 LPTIMER_ARR(偏移:1Ch)             | 263     |

|    | 15.6.9  | LPTIMER 捕捉比较寄存器 1 LPTIMER_CCR1(偏移: 20h)         | 263     |

|    | 15.6.10 | LPTIMER 捕捉比较寄存器 2 LPTIMER_CCR2(偏移:24h)          | 263     |

|    | 15.6.11 | LPTIMER 计数值 load 寄存器 LPTIMER_LOAD(偏移:28h)       | 263     |

|    | 15.6.12 | LPTIMER 计数缓存寄存器 LPTIMER_BUFFER(偏移:2Ch)          | 263     |

|    | 15.7 使原 | <b>目流程</b>                                      | 264     |

|    | 15.7.1  | 普通定时器                                           | 264     |

|    | 15.7.2  | 结合 DMA 输入捕获功能                                   | 264     |

|    | 15.7.3  | PWM 输出                                          | 265     |

|    | 15.7.4  | ETR 脉冲触发计数模式                                    |         |

|    | 15.7.5  | ETR 脉冲计数模式                                      | 266     |

|    | 15.7.6  | Timeout 模式                                      | 266     |

| 16 | DMA     |                                                 | 268     |

|    | 16.1 概〕 | ₫                                               | 268     |

|    | 16.2 主  | 要特性                                             | 268     |

|    | 16.3 寄花 | 字器描述                                            | 268     |

|    | 16.3.1  | DMA 通道源传送地址寄存器 (DMA_SRCADDR_Cx) (偏移: 20*x+00h)  | (x=0,1) |

|    |         |                                                 | 269     |

|    | 16.3.2  | DMA 通道目的传送地址寄存器 (DMA_DSTADDR_Cx) (偏移: 20*x+04h) | (x=0,1) |

|    |         |                                                 | 269     |

|    | 16.3.3  | DMA 通道控制信息寄存器(DMA_CHCTRL_Cx)(偏移: 20*x+08h)(x    | =0,1)   |

|    |         |                                                 | 269     |

|    | 16.3.4  | DMA 通道传送状态寄存器(DMA_CHSTS_Cx)(偏移: 20*x +0Ch)(x=   | =0,1)   |

|    |         |                                                 | 271     |

|    | 16.3.5  | DMA 通道源外设选择寄存器(DMA_CHSPER_Cx)(偏移: 20*x +10h)    | (x=0,1) |

|    |         |                                                 | 271     |

|    | 16.3.6  | DMA 通道目标外设选择寄存器 (DMA_CHDPER_Cx) (偏移: 20*x +14h) | (x=0,1) |

|    |         |                                                 | 272     |

V1.0.1

|    | 16.3.7  | DMA 控制器使能寄存器(DMA_EN)(偏移:40h)         | 274 |

|----|---------|--------------------------------------|-----|

|    | 16.3.8  | DMA 软复位寄存器(DMA_SOFT_RESET)(偏移: 44h)  | 274 |

|    | 16.3.9  | DMA 中断指示寄存器(DMA_INT_STATUS)(偏移: 48h) | 274 |

|    | 16.3.10 | DMA 中断屏蔽寄存器(DMA_INT_MASK)(偏移: 4Ch)   | 274 |

|    | 16.3.11 | DMA 外设请求状态寄存器(DMA_PER_REQ)(偏移:54h)   | 275 |

|    | 16.4 使月 | 用流程                                  | 276 |

| 17 | CRC     |                                      | 277 |

|    |         | 术                                    |     |

|    | 17.2 寄存 | 字器描述                                 | 277 |

|    | 17.2.1  | 数据寄存器 CRC_DATA(偏移: 00H)              | 277 |

|    | 17.2.2  | 初始值寄存器 CRC_INIT(偏移: 04H)             | 278 |

|    | 17.2.3  | 控制寄存器 CRC_CTRL (偏移: 08H)             | 278 |

|    | 17.3 使月 | 用流程                                  | 278 |

| 18 | RNG     |                                      | 279 |

|    |         | 术                                    |     |

|    |         |                                      |     |

|    | 18.3 寄存 | 字器描述                                 | 279 |

|    | 18.3.1  | 随机数控制寄存器 RNG_CR(偏移: 0E0h)            | 279 |

|    | 18.3.2  | 随机数种子寄存器 RNG_SEED(偏移: 0E4h)          | 279 |

|    | 18.3.3  | 随机数数据寄存器 RNG_DATA(偏移: 0E8h)          | 280 |

|    | 18.4 使月 | 用流程                                  | 280 |

| 19 | WDT     |                                      | 281 |

| 17 |         | 术                                    |     |

|    |         |                                      |     |

|    |         | 字器描述                                 |     |

|    | 19.3.1  | <br>装载寄存器 WDT_LOAD(偏移: 00h)          |     |

|    | 19.3.2  | -<br>计数寄存器 WDT_CNT(偏移: 04h)          |     |

|    | 19.3.3  | -<br>控制寄存器 WDT_CTRL(偏移: 08h)         |     |

|    | 19.3.4  | 清除寄存器 WDT_CLR(偏移: 0ch)               | 282 |

|    | 19.3.5  | RAW 中断状态寄存器 WDT_INTRAW(偏移:10h)       | 283 |

|    | 19.3.6  | MASK 中断状态寄存器 WDT_MINTS(偏移:14h)       | 283 |

|    | 19.3.7  | STALL 控制寄存器 WDT_STALL(偏移: 18h)       | 283 |

|    | 19.3.8  | LOCK 寄存器 WDT_LOCK(偏移: 1ch)           | 283 |

|    | 19.4 使月 | 用流程                                  | 284 |

|    | 19.4.1  | WDT 定时器配置                            | 284 |

|    | 19.4.2  | WDT 喂狗流程配置                           | 284 |

| 20 | WWDT    |                                      | 285 |

|    |         |                                      |     |

| 20.2       主要特性                             | 285<br>286<br>286<br>286 |

|---------------------------------------------|--------------------------|

| 20.3.1 控制寄存器 WWDT_CON(偏移:00h)               | 286<br>286<br>286<br>287 |

| <del>-</del>                                | 286<br>286<br>287        |

| 20.3.2 配置寄存器 WWDT CFG(偏移:04h)               | 286<br>287               |

|                                             | 287                      |

| 20.3.3 计数寄存器 WWDT_CNT(偏移:08h)               |                          |

| 20.3.4 中断使能寄存器 WWDT_IE(偏移:0ch)              | 287                      |

| 20.3.5 中断标志寄存器 WWDT_IF(偏移:10h)              | 207                      |

| 20.4 使用流程                                   | 287                      |

| 21 ADC                                      | 288                      |

| 21.1 概述                                     |                          |

| 21.2 主要特性                                   |                          |

|                                             |                          |

| 21.4 寄存器描述                                  |                          |

| 21.4.1 ADC 中断和状态寄存器(ADC_ISR)(偏移: 000h)      |                          |

|                                             |                          |

|                                             |                          |

| 21.4.4 ADC 配置寄存器(ADC_CFGR)(偏移: 00Ch)        | 293                      |

| 21.4.5 ADC 采样时间控制寄存器(ADC_SMTR)(偏移:010h)     |                          |

| 21.4.6 ADC 通道控制寄存器(ADC_CHER)(偏移:014h)       | 296                      |

| 21.4.7 ADC 通道选择寄存器(ADC_SEQ)(偏移: 018h)       | 297                      |

| 21.4.8 ADC 模拟看门狗阈值寄存器(ADC_HLTR)(偏移:020h)    | 297                      |

| 21.4.9 ADC 注入通道控制寄存器(ADC_IJCHER)(偏移: 024h)  | 297                      |

| 21.4.10 ADC 注入通道选择寄存器(ADC_IJSEQ)(偏移:028h)   | 298                      |

| 21.4.11 ADC 数据寄存器 0(ADC_DR0)(偏移: 030h)      | 298                      |

| 21.4.12 ADC 数据寄存器 1(ADC_DR1)(偏移: 034h)      | 299                      |

| 21.4.13 ADC 数据寄存器 2(ADC_DR2)(偏移: 038h)      | 299                      |

| 21.4.14 ADC 数据寄存器 3(ADC_DR3)(偏移: 03Ch)      | 299                      |

| 21.4.15 ADC 数据寄存器 4(ADC_DR4)(偏移: 040h)      | 299                      |

| 21.4.16 ADC 数据寄存器 5(ADC_DR5)(偏移:044h)       | 299                      |

| 21.4.17 ADC 数据寄存器 6(ADC_DR6)(偏移:048h)       | 299                      |

| 21.4.18 ADC 数据寄存器 7(ADC_DR7)(偏移:04Ch)       | 300                      |

| 21.4.19 ADC 注入通道数据寄存器 0(ADC_IJDR0)(偏移:050h) | 300                      |

| 21.4.20 ADC 注入通道数据寄存器 1(ADC_IJDR1)(偏移:054h) | 300                      |

| 21.4.21 ADC 注入通道数据寄存器 2(ADC_IJDR2)(偏移:058h) | 300                      |

| 21.4.22 ADC 注入通道数据寄存器 3(ADC_IJDR3)(偏移:05Ch) | 300                      |

| 21.4.23 ADC 过采样平均结果寄存器(ADC_DR_OVS)(偏移:060h) | 300                      |

| 21.4.24 ADC 硬件触发使能配置寄存器(ADC_HDT)(偏移:0A8h)   | 301                      |

|    | 21.4.25   | ADC 注入通道硬件触发使能配置寄存器(ADC_IJHDT)(偏移:0ACh)    | 303 |

|----|-----------|--------------------------------------------|-----|

|    | 21.4.26   | ADC 通道采样时间配置寄存器 0(ADC_SMTR0)(偏移:0B0h)      | 305 |

|    | 21.4.27   | ADC 通道采样时间配置寄存器 1(ADC_SMTR1)(偏移:0B4h)      | 306 |

|    | 21.4.28   | ADC 注入通道采样时间配置寄存器(ADC_IJSMTR)(偏移:0B8h)     | 307 |

|    | 21.5 ADC  | 使用流程                                       | 309 |

|    | 21.5.1    | 单次扫描模式单通道 A/D 转换                           | 309 |

|    | 21.5.2    | 单次扫描模式多通道 A/D 转换                           | 309 |

|    | 21.5.3    | 连续扫描模式单通道 A/D 转换                           | 310 |

|    | 21.5.4    | 连续扫描模式多通道 A/D 转换                           | 311 |

|    | 21.5.5    | 硬件触发事件 A/D 转换                              | 312 |

|    | 21.5.6    | 注入通道普通注入模式 A/D 转换                          | 313 |

|    | 21.5.7    | 注入通道自动注入模式 A/D 转换                          | 314 |

|    | 21.5.8    | 注意事项                                       | 315 |

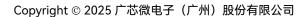

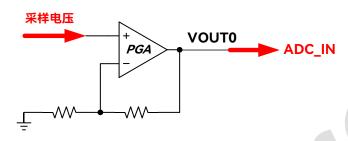

|    | 21.6 ADC  | 经 PGA 缓冲采样使用流程                             | 316 |

|    | 21.6.1    | ADC 经 PGA 缓冲采样图                            | 316 |

|    | 21.6.2    | ADC 经 PGA 缓冲采样流程图                          | 316 |

|    | 21.6.3    | ADC 经 PGA 缓冲后采样使用流程                        | 316 |

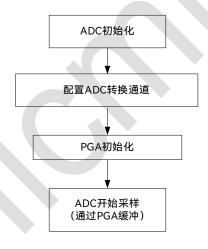

| 22 | COMP      |                                            | 317 |

|    |           | 术                                          |     |

|    |           |                                            |     |

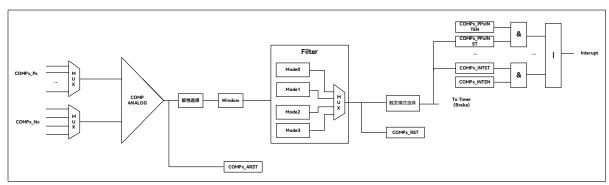

|    |           | P 功能框图                                     |     |

|    |           | P 滤波模式                                     |     |

|    | 22.4.1    | Mode 1                                     | 319 |

|    | 22.4.2    | Mode 2                                     | 319 |

|    | 22.4.3    | Mode 3                                     | 319 |

|    | 22.4.4    | Mode 4                                     | 320 |

|    | 22.5 Wind | ow 功能                                      | 320 |

|    | 22.6 寄存   | 字器描述                                       | 320 |

|    | 22.6.1    | COMP0 控制寄存器 COMP0_CFG(偏移: 118h)            | 321 |

|    | 22.6.2    | COMP1 控制寄存器 COMP1_CFG(偏移: 11Ch)            | 322 |

|    | 22.6.3    | COMP0 轮询寄存器 COMP0_POLL(偏移: 128h)           | 323 |

|    | 22.6.4    | COMP1 轮询寄存器 COMP1_POLL(偏移:12Ch)            | 324 |

|    | 22.6.5    | COMP0 轮询 MASK 寄存器 COMP0_POLLMASK(偏移: 138h) | 325 |

|    | 22.6.6    | COMP1 轮询 MASK 寄存器 COMP1_POLLMASK(偏移: 13Ch) | 325 |

|    | 22.6.7    | COMP0 滤波设置寄存器 COMP0_LVSET(偏移: 148h)        | 325 |

|    | 22.6.8    | COMP1 滤波设置寄存器 COMP1_LVSET(偏移: 14Ch)        | 326 |

|    | 22.6.9    | COMP0 WINDOW 设置寄存器 COMP0_WINCFG(偏移: 158h)  | 326 |

|    | 22.6.10   | COMP1 WINDOW 设置寄存器 COMP1_WINCFG(偏移:15Ch)   | 329 |

|    |           |                                            |     |

|    | 22.6.   | 11 COMP0 状态寄存器 COMP0_INTSTAT(偏移:168h) | 331 |

|----|---------|---------------------------------------|-----|

|    | 22.6.   | 12 COMP1 状态寄存器 COMP1_INTSTAT(偏移:16Ch) | 332 |

|    | 22.6.   | 13 COMP0 中断使能寄存器 COMP0_INTEN(偏移:178h) | 332 |

|    | 22.6.   | 14 COMP1 中断使能寄存器 COMP1_INTEN(偏移:17Ch) | 333 |

|    | 22.7    | 使用流程                                  | 333 |

| 23 | DIV     |                                       | 335 |

|    | 23.1 柞  | 既述                                    | 335 |

|    | 23.2    | 主要特性                                  | 335 |

|    | 23.3    | 寄存器描述                                 | 335 |

|    | 23.3.   | 1 被除数寄存器 DIV_DIVIDEND(偏移:00h)         | 335 |

|    | 23.3.   | 2 除数寄存器 DIV_DIVISOR(偏移: 04h)          | 336 |

|    | 23.3.   | 3 余数寄存器 DIV_REMAIN(偏移: 08h)           | 336 |

|    | 23.3.4  | 4 商寄存器 DIV_QUOTIENT(偏移: 0Ch)          | 336 |

|    | 23.3.   | 5 状态寄存器 DIV_STATUS(偏移: 10h)           | 336 |

|    | 23.4    | 吏用流程                                  | 336 |

| 24 | SQRT    |                                       | 337 |

|    | 24.1 柞  | 既述                                    | 337 |

|    | 24.2    | 主要特性                                  | 337 |

|    | 24.3    | 寄存器描述                                 | 337 |

|    | 24.3.   | 1 SQRT 被开方数据寄存器(SQRT_VALUE)(偏移:00h)   | 337 |

|    | 24.3.   | 2 SQRT 开方运算结果寄存器(SQRT_RESULT)(偏移:04h) | 337 |

|    | 24.3.   | 3 SQRT 状态寄存器(SQRT_SR)(偏移:08h)         | 338 |

|    | 24.4    | 吏用流程                                  | 338 |

| 25 | SysTick |                                       | 339 |

|    | 25.1 柞  | 既述                                    | 339 |

|    | 25.2    | 寄存器描述                                 | 339 |

|    | 25.2.   | 1 控制和状态寄存器 SysTick_CTRL(偏移: 00h)      | 340 |

|    | 25.2.   | 2 重载值寄存器 SysTick_LOAD(偏移:04h)         | 340 |

|    | 25.2.   | 3 当前值寄存器 SysTick_VAL(偏移: 08h)         | 340 |

|    | 25.3 f  | 使用流程                                  | 341 |

| 26 | 调试支持    | 寺(DBG)                                | 342 |

| 27 | 版太维排    | à                                     | 343 |

# 图目录

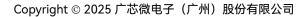

| 图 | 3-1:  | 总线架构图                                    | 7   |

|---|-------|------------------------------------------|-----|

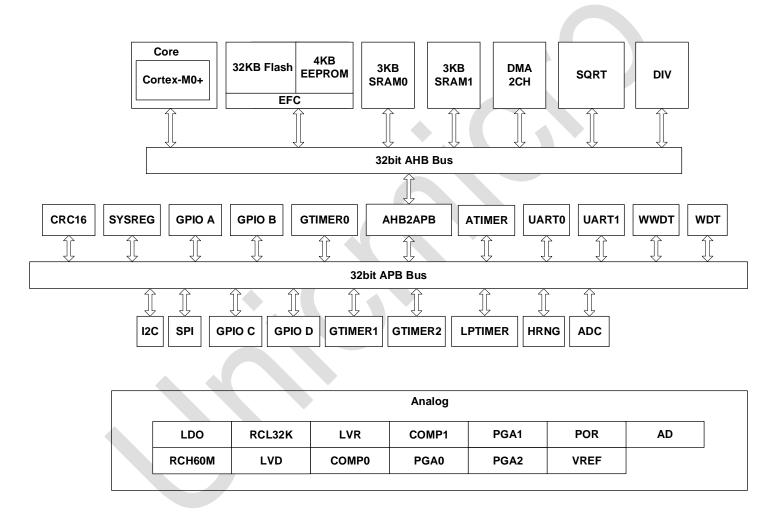

| 图 | 3-2:  | 存储器地址映射图                                 | 8   |

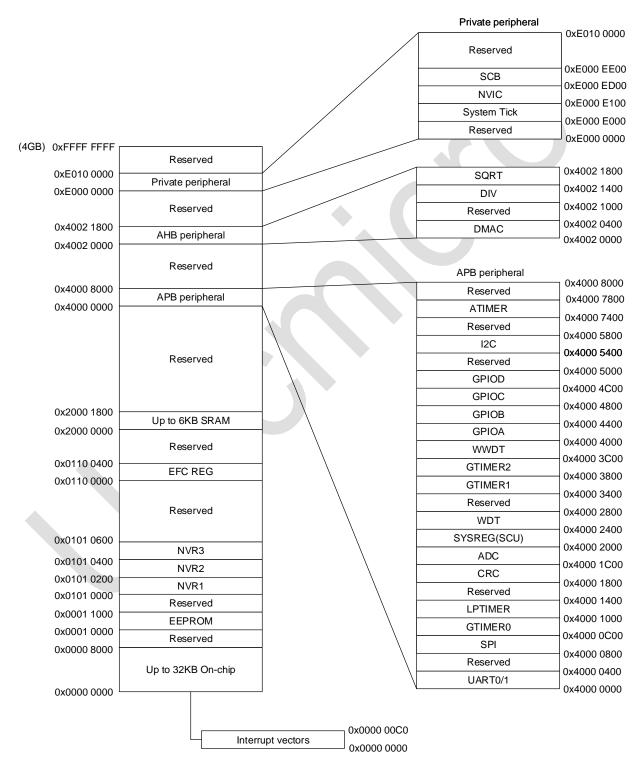

| 冬 | 4-1:  | Cortex-M0+处理器功能框图                        | 11  |

| 冬 | 4-2:  | Cortex-M0+的寄存器组                          | 11  |

| 冬 | 5-1:  | 时钟模块框图                                   | 12  |

| 冬 | 6-1:  | eFlash 存储区域                              | 57  |

| 冬 | 6-2:  | EEPROM8 关键字配置图                           | 58  |

| 冬 | 6-3:  | 写操作流程                                    | 66  |

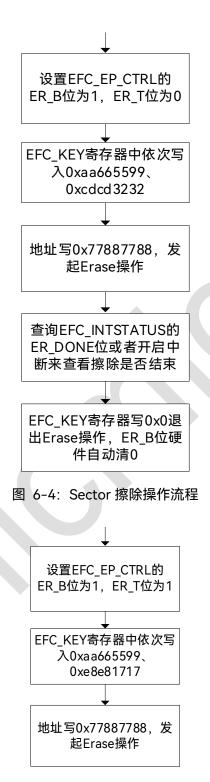

| 图 | 6-4:  | Sector 擦除操作流程                            | 67  |

| 图 | 6-5:  | Chip 擦除操作流程                              | 67  |

| 冬 | 10-1: | 主机发送流程图                                  | 94  |

| 冬 | 10-2: | 主机接收流程图                                  | 95  |

| 图 | 10-3  | 从机发送流程图                                  | 96  |

|   |       | 从机接收流程图                                  |     |

|   |       | ATIMER 结构框图                              |     |

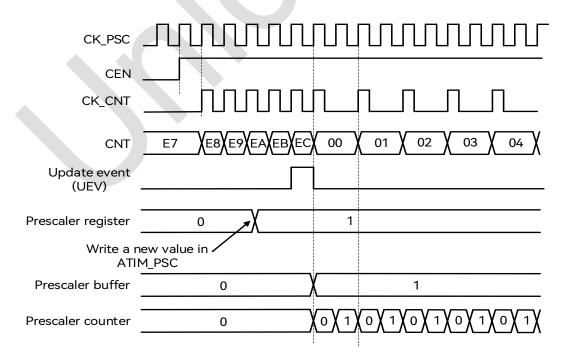

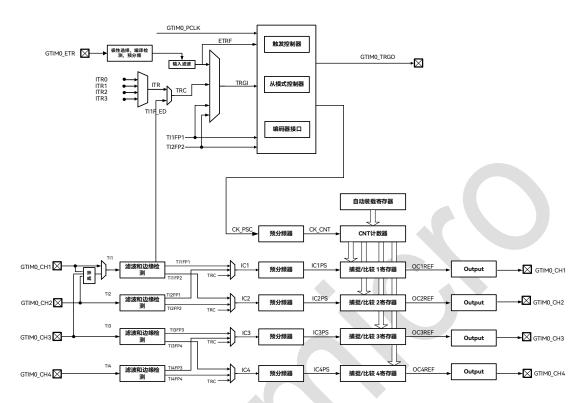

|   |       | 预分频从 1 变为 2 的波形                          |     |

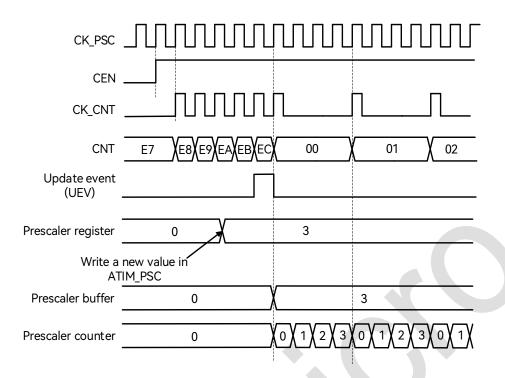

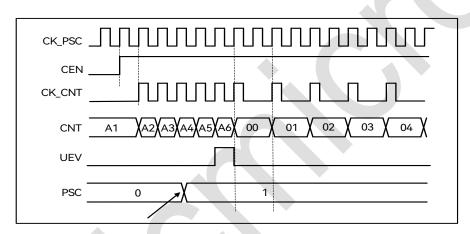

| 冬 | 12-3: | 预分频从 1 变为 4 的波形                          | 113 |

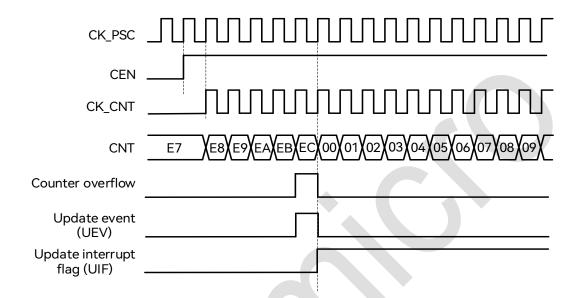

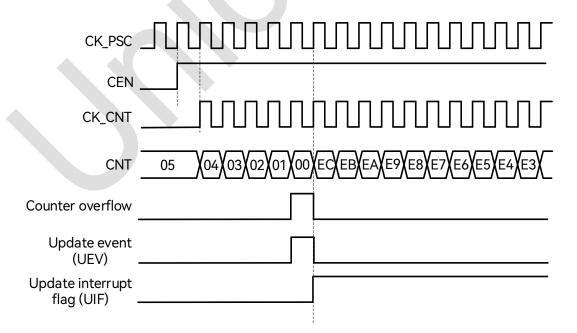

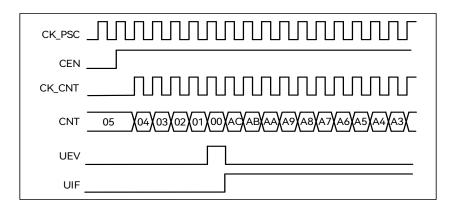

| 冬 | 12-4: | 向上计数波形,内部时钟不分频                           | 114 |

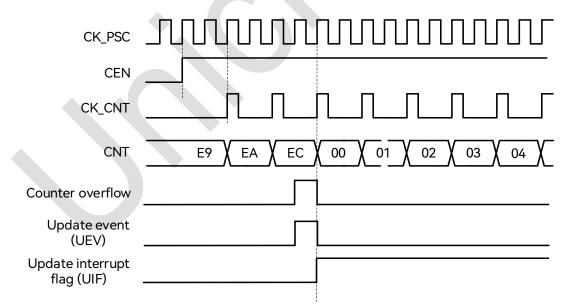

| 图 | 12-5: | 向上计数波形,内部时钟 2 分频                         | 114 |

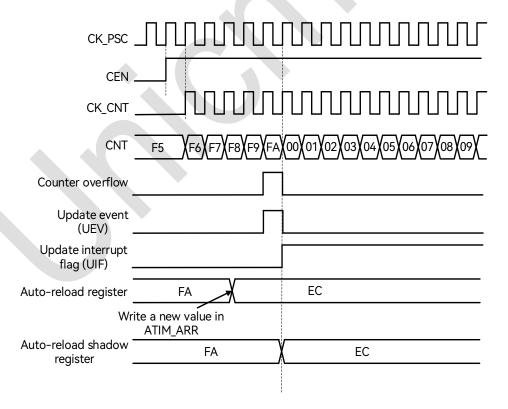

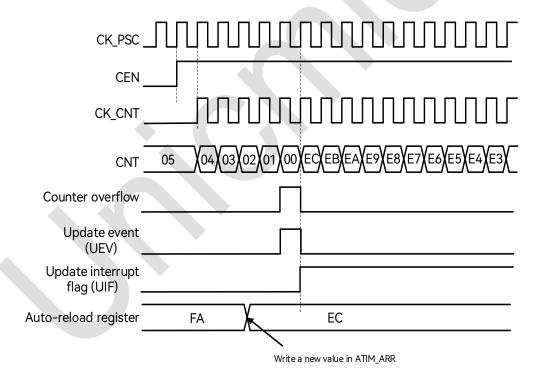

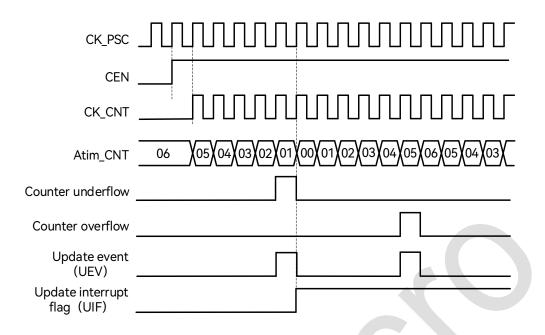

| 冬 | 12-6  | ARPE=0(ATIMER_ARR 没有预装载)时的更新事件           | 115 |

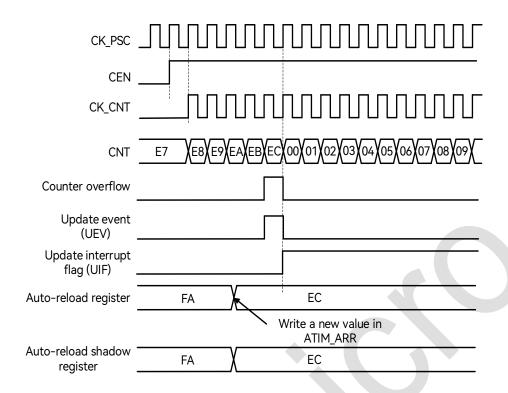

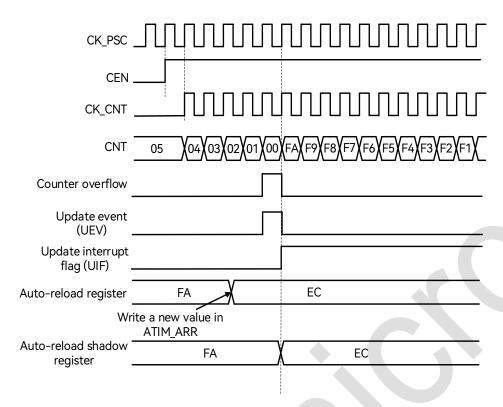

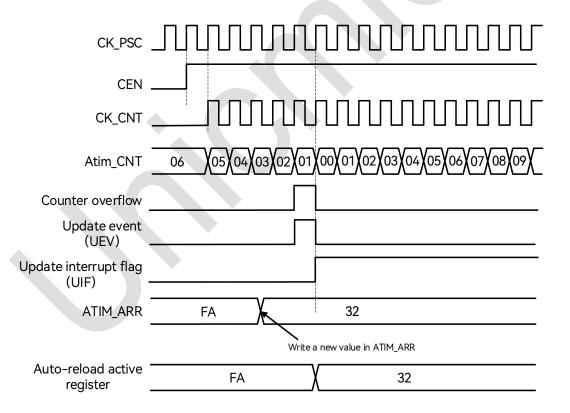

| 图 | 12-7: | ARPE=1(ATIMER_ARR 预装载)时的更新事件             | 115 |

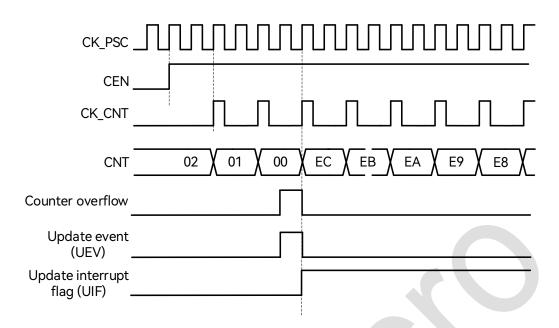

| 冬 | 12-8: | 向下计数,内部时钟不分频                             | 116 |

| 冬 | 12-9: | 向下计数,内部时钟 2 分频                           | 117 |

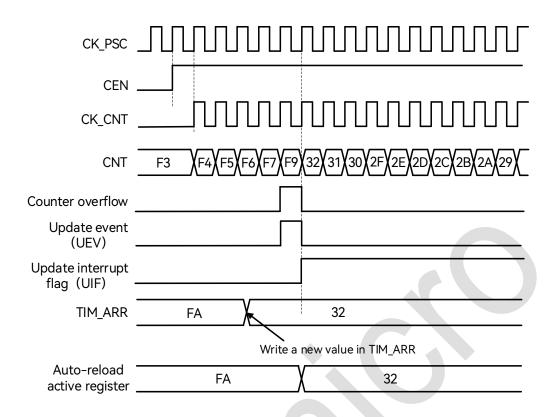

| 图 | 12-10 | D: ARPE=0(ATIMER_ARR 没有预装载)时的更新事件        | 117 |

| 图 | 12-1  | 1:ARPE=1(ATIMER_ARR 预装载)时的更新事件           | 118 |

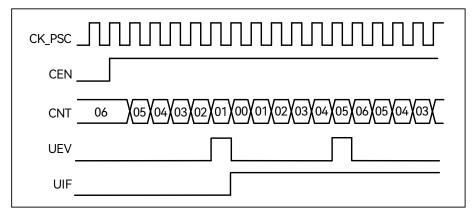

|   |       | 2:中心对齐计数器时序图,ATIMER_PSC=0,ATIMER_ARR=0x6 |     |

| 图 | 12-13 | 3:计数器时序图,ARPE=1 时的更新事件(计数器下溢)            | 119 |

| 冬 | 12-14 | 4:计数器时序图,ARPE=1 时的更新事件(计数器溢出)            | 120 |

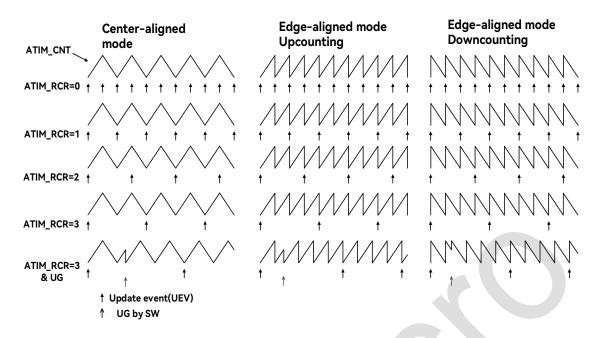

| 图 | 12-1  | 5:不同模式下更新速率的例子,及 ATIMER_RCR 的寄存器设置       | 121 |

| 图 | 12-1  | 5:内部时钟源模式,时钟分频因子为 1                      | 122 |

| 图 | 12-17 | 7:外部时钟连接例子                               | 123 |

| 图 | 12-18 | 3:外部时钟模式 1 下的时序                          | 123 |

| 图 | 12-19 | 9:外部时钟模式 1 下的时序                          | 124 |

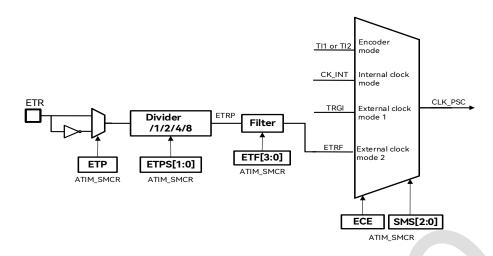

| 图 | 12-20 | D: 外部触发输入框图                              | 125 |

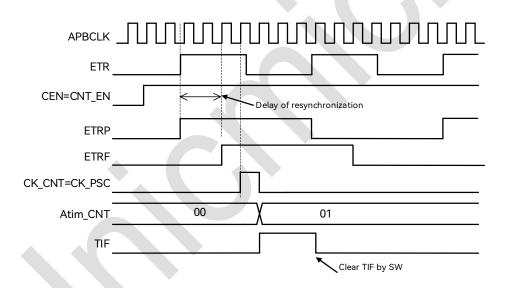

| 图 | 12-2  | 1:外部时钟模式 2 下的时序 1                        | 125 |

| 冬 | 12-22 | 2: 外部时钟模式 2 下的时序                         | 126 |

|   |       |                                          |     |

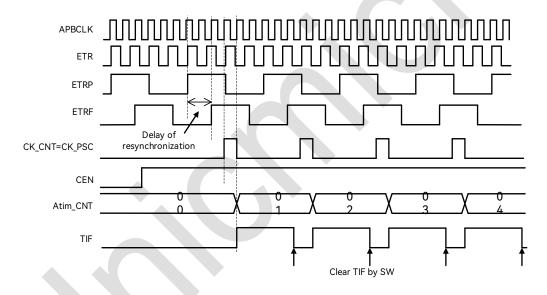

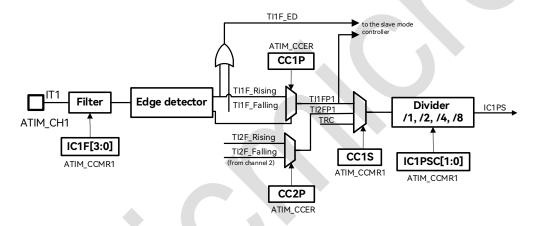

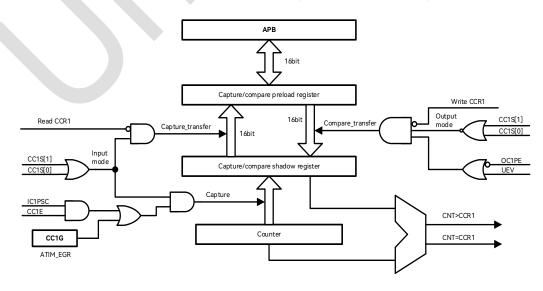

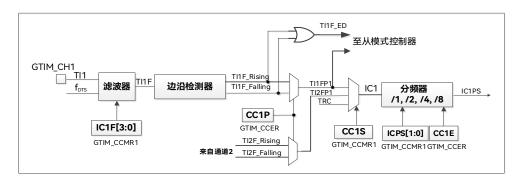

| 图 | 12-23:  | 捕获/比较通道(通道 1 输入部分)              | 127 |

|---|---------|---------------------------------|-----|

| 图 | 12-24:  | 捕获/比较通道 1 的主电路                  | 127 |

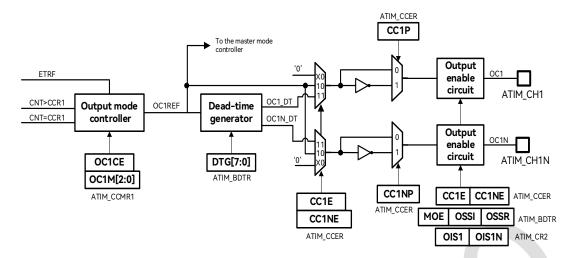

| 图 | 12-25:  | 捕获/比较通道的输出部分(通道 1 至 3)          | 128 |

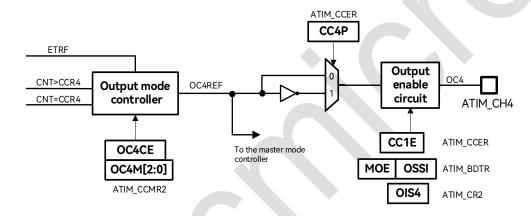

| 图 | 12-26:  | 捕获/比较通道的输出部分(通道 4)              | 128 |

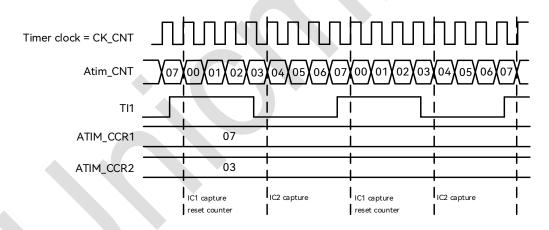

| 冬 | 12-27:  | PWM 输入捕获模式时序                    | 129 |

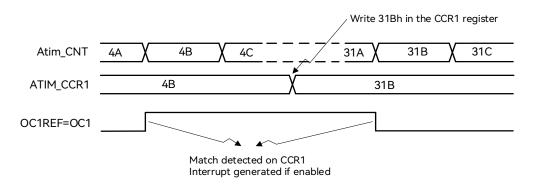

| 冬 | 12-28:  | 输出比较模式,翻转 OC1                   | 131 |

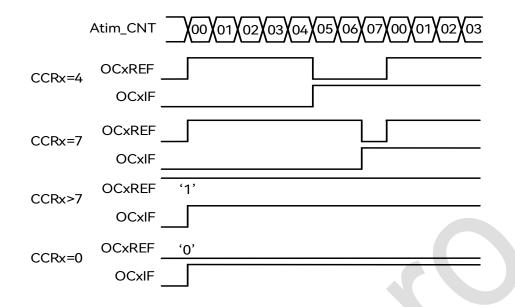

| 冬 | 12-29:  | 边沿对齐的 PWM 波形(ARR=7)             | 132 |

| 冬 | 12-30:  | 中央对齐的 PWM 波形(ARR=7)             | 133 |

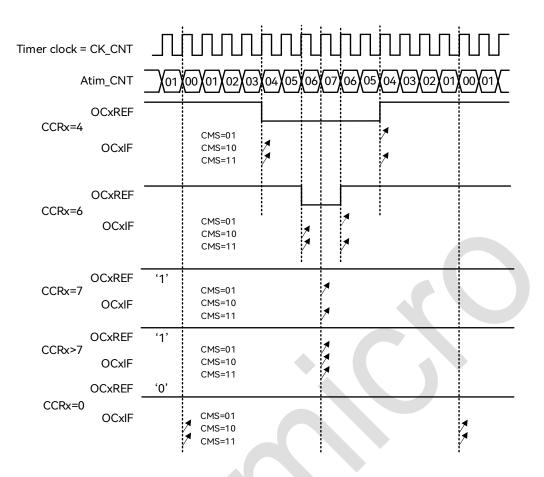

| 冬 | 12-31:  | 移相模式的 PWM 波形(ARR=7)             | 134 |

| 冬 | 12-32:  | 带死区插入的互补输出                      | 134 |

| 图 | 12-33:  | 死区波形延迟大于负脉冲                     | 134 |

| 图 | 12-34:  | 死区波形延迟大于正脉冲                     | 135 |

| 图 | 12-35:  | 响应刹车的输出                         | 136 |

| 图 | 12-36:  | 产生六步 PWM,使用 COM 的例子(OSSR=1)     | 137 |

| 图 | 12-37:  | 单脉冲模式的例子                        | 138 |

| 图 | 12-38:  | ETR 信号清除 ATIMER 的 OCxREF        | 139 |

| 冬 | 12-39:  | 编码器模式下的计数器操作实例                  | 140 |

| 冬 | 12-40:  | 复位模式下的时序                        | 141 |

|   |         | 门控模式下的时序                        |     |

| 图 | 12-42:  | 触发器模式下的时序                       | 143 |

|   |         | 外部时钟模式 2 和触发模式下的时序              |     |

|   |         | GTIMER 结构框图                     |     |

| 图 | 13-2: ( | GTIMER 预分频从 1 变为 2 的波形图         | 179 |

|   |         | 句上计数波形图                         |     |

|   |         | 句下计数图                           |     |

| 图 | 13-5:   | 中心对齐计数器时序图                      | 182 |

| 图 | 13-6: / | APBCLK 时钟源模式,时钟分频因子为 1          | 183 |

| 图 | 13-7: ‡ | 甫获/比较通道(通道 1 输入部分)              | 185 |

| 冬 | 13-8: } | 甫获/比较通道 1 的主电路                  | 185 |

| 图 | 13-9: ‡ | 甫获/比较通道的输出部分                    | 185 |

| 冬 | 13-10:  | PWM 输入捕获                        | 187 |

| 图 | 13-11:  | 输出比较模式,翻转 OC1                   | 188 |

| 图 | 13-12:  | 边沿对齐的 PWM 波形(ARR=7)             | 189 |

| 图 | 13-13:  | 中央对齐的 PWM 波形(APR=7)             | 190 |

|   |         | 单脉冲模式的例子                        |     |

|   |         | GTIMER_ETR 信号清除 GTIMER 的 OCxREF |     |

|   |         | 编码器模式下的计数器操作实例                  |     |

|   |         | 复位模式下的时序                        |     |

| 图 13-18: 门控模式下的时序图                     | 196 |

|----------------------------------------|-----|

| 图 13-19: 触发器模式下的时序                     | 197 |

| 图 14-1: GTIMER 结构框图                    | 217 |

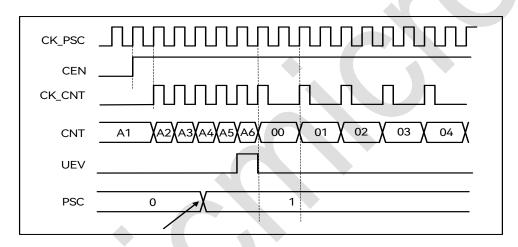

| 图 14-2: GTIMER 预分频从 1 变为 2 的波形图        | 218 |

| 图 14-3: 向上计数波形图                        | 219 |

| 图 14-4: 向下计数图                          | 220 |

| 图 14-5: 中心对齐计数器时序图                     | 220 |

| 图 14-6: APBCLK 时钟源模式,时钟分频因子为 1         | 221 |

| 图 14-7: 捕获/比较通道(通道 1 输入部分)             | 223 |

| 图 14-8: 捕获/比较通道 1 的主电路                 |     |

| 图 14-9: 捕获/比较通道的输出部分                   | 224 |

| 图 14-10: PWM 输入捕获                      |     |

| 图 14-11: 输出比较模式, 翻转 OC1                | 226 |

| 图 14-12: 边沿对齐的 PWM 波形(ARR=7)           | 227 |

| 图 14-13: 中央对齐的 PWM 波形 (APR=7)          |     |

| 图 14-14: 单脉冲模式的例子                      | 230 |

| 图 14-15: GTIMER_ETR 信号清除 GTIMER 的 OCxR |     |

| 图 14-16: 编码器模式下的计数器操作实例                |     |

| 图 14-17: 复位模式下的时序                      |     |

| 图 14-18: 门控模式下的时序图                     | 234 |

| 图 14-19: 触发器模式下的时序                     |     |

| 图 15-1: LPTIMER 结构框图                   | 256 |

| 图 21-1: ADC 经 PGA 缓冲采样图                | 316 |

| 图 21-2: ADC 经 PGA 缓冲采样流程图              | 316 |

| 图 22-1: COMP 模拟功能框图                    | 318 |

| 图 22-2: COMP 整休功能框图                    | 310 |

# 表目录

| 表 | 3-1:  | 存储器和模块地址分配             | 9   |

|---|-------|------------------------|-----|

| 表 | 5-1:  | 系统时钟选择                 | 12  |

| 表 | 5-2:  | 系统复位源                  | 13  |

| 表 | 5-3:  | 低功耗模式                  | 15  |

| 表 | 5-4:  | 系统寄存器列表                | 18  |

| 表 | 6-1:  | EFC 寄存器列表              | 59  |

| 表 | 7-1:  | 中断源                    | 69  |

| 表 | 8-1:  | GPIO 寄存器列表             | 70  |

| 表 | 9-1:  | UART0/1 寄存器列表          | 77  |

| 表 | 10-1  | I2C 寄存器列表              | 83  |

| 表 | 11-1: | SPI 寄存器列表              | 99  |

| 表 | 11-2  | SPI 两种引脚搭配方式表          | 107 |

| 表 | 12-1  | 输入信号源                  | 127 |

|   |       | Encoder Interface 计数方式 |     |

| 表 | 12-3  | DMA 访问计数方式             | 144 |

|   |       | ATIMER 寄存器列表           |     |

|   |       | GTIMER0/1/2 内部信号扩展表    |     |

|   |       | 编码计数方式与输入信号            |     |

| 表 | 13-3  | GTIMER 寄存器列表           | 198 |

|   |       | GTIMER0/1/2 内部信号扩展表    |     |

| 表 | 14-2  | 编码计数方式与输入信号            | 232 |

| 表 | 14-3  | GTIMER 寄存器列表           | 236 |

| 表 | 15-1: | LPTIMER 寄存器列表          | 258 |

| 表 | 17-1: | CRC 寄存器列表              | 277 |

| 表 | 18-1: | RNG 寄存器列表              | 279 |

| 表 | 19-1: | WDT 寄存器列表              | 281 |

| 表 | 20-1  | WWDT 寄存器列表             | 285 |

| 表 | 21-1  | ADC 管脚分布               | 289 |

| 表 | 21-2  | ADC 寄存器列表              | 289 |

| 表 | 22-1  | COMP 寄存器列表             | 320 |

| 表 | 23-1  | DIV 寄存器列表              | 335 |

| 表 | 24-1  | SQRT 寄存器列表             | 337 |

| 表 | 25-1  | SysTick 寄存器列表          | 339 |

UM32Mx56 用户手册 文档约定

# 1 文档约定

# 1.1 寄存器相关缩写词列表

寄存器说明中使用以下缩写词:

| R/W   | 可读可写,软件可以读写该位                      |

|-------|------------------------------------|

| R     | 只读,软件只能读取该位                        |

| W     | 只写,软件只能写入该位,软件读返回复位值               |

| RC    | 读清 0                               |

| R/W1C | 可读,写 1 清零软件可以读取该位。写 1 清除该位,写 0 无效  |

| R/W0C | 可读,写 0 清除,软件可以读取该位。写 0 清除该位,写 1 无效 |

| RSV   | 保留位,必须保持复位值                        |

# 1.2 词汇表

本节简要介绍本文档中所用首字母缩略词和缩写词的定义:

● CPU 内核集成了 SWD 调试端口 (SWD-DP): 提供基于串行线调试 (SWD) 协议的 2 引脚 (时钟和数据)接口。

● 字: 32 位数据/指令。

● 半字: 16 位数据/指令。

● 字节:8位数据。

● 双字: 64 位数据。

● IAP(在应用中编程): IAP 是指可以在用户程序运行期间对微控制器的 Flash 进行重新编程。

● ICP (在线编程): ICP 是指可以在器件安装于用户应用电路板上时使用 JTAG 协议、SWD 协议 或自举程序对微控制器的 Flash 进行编程。

● 选项字节:存储于 Flash 中的产品配置位。

● OBL: 选项字节加载器。

● AHB: 高级高性能总线。

● APB: 低速外设总线

# 2 产品简介

## 2.1 系统概述

UM32Mx56 系列芯片是广芯微电子(广州)股份有限公司研制的基于 ARM Cortex-M0+内核的 Low Pin Count、宽电压工作范围的 32 位处理器 SoC 芯片系列,重点面向汽车电动化、智能家居、电机控制及工业控制等应用场景。依据行业应用场景的具体应用需求,芯片内部集成了 12 位 SAR ADC、UART、SPI、I2C 等通用外围通讯接口,ADC、PGA、COMP 等传感获取接口,LPTIMER、WDT 等超低功耗模块接口,以及 SQRT、DIV 除法器等硬件算法模块。具有高整合度、高抗干扰、高可靠性和超低功耗等技术特点。内置 RC 高频和低频振荡器,支持免晶振应用。支持 Keil MDK 集成开发环境、支持 C 语言和汇编语言进行软件开发。

UM32Mx56 系列芯片增加了芯片内数据防盗取等安全特性,增加了 SWD 读保护、SWD 接口物理禁止等功能。芯片内部 eFlash 存储器增加 ECC 纠错码和数据加密功能,ECC 纠错可以有效防止 eFlash 数据由于环境因素丢失或偶发读错误的现象。此外,芯片内部增加对部分 EEPROM 区和32KB eFlash 主存储区的防擦写机制,可以有效防止客户应用数据、程序被改写。

#### 典型应用场景:

- 电机控制

- 工业物联网应用

- 智能交通,智慧城市,智能家居

- 智能门锁,资产追踪、无线监控等智能传感器终端应用

## 2.2 主要特性

#### ● 超低功耗电源管理系统

- ▶ 低功耗模块 LPTIMER、WDT

- ▶ 内置 ROSC/LDO/POR,可免晶振/LDO/复位电路

#### ● 处理器

- ▶ 32 位 ARM Cortex-M0+, 系统最高主频 60MHz

- 单周期硬件乘法器

#### ● 存储器

- > 32KB FLASH

- ➤ 4KB EEPROM

- ➢ 6KB SRAM

- > Sector 大小: 512B, 擦写次数: 100,000 次

- ▶ 数据保存时间: 10年@常温

#### ● 时钟

- ▶ 内部高速时钟 60MHz

- ▶ 内部低速时钟 32kHz

#### ● 模拟外设

- ▶ 1 个 12 位 1Msps ADC 转换器, 多达 16 通道

- ▶ 3个运算放大器

- ▶ 2个电压比较器

#### ● 通信接口

- ▶ 最大 2 路 UART 串口

- ▶ 1 路通用的 SPI 接口

- ▶ 1路I2C接口

#### ● 定时器

- ▶ 1个16位高级定时器 ATIMER 支持输入捕获、死区互补 PWM 输出

- ▶ 1 个 32 位通用定时器、2 个 16 位通用定时器 GTIMER 支持输入捕获、PWM 输出

- ▶ 1 个 32 位低功耗定时器 LPTIMER 支持 2 路 PWM 输出

- ▶ 1个32位低功耗看门狗 WDT, 可复位/中断

- ▶ 1 个 18 位窗口看门狗 WWDT, 可复位/中断

- ▶ 最大共支持 21 路 PWM 输出

#### ● GPIO 通用输入/输出端口

- ▶ 最大 26 个通用输入/输出管脚

- ▶ 支持边沿/电平触发中断

- ▶ 16/8mA 两档驱动能力可配置

#### ● 安全功能

- ➤ 低电压检测 LVD

- ▶ 掉电复位 LVR, 防死机设计

- > CRC16-CCITT 数据校验算法硬件加速

- ➤ RNG 硬件随机数发生器

- > 16 字节全球唯一芯片序列号 ID

#### ● 硬件加速引擎

- ▶ 除法器 DIV, 8 个周期出结果

- ▶ 开方运算,4个周期出结果

#### ● 支持 SIP 预驱

- ➤ UM32xxx

- ✓ 内置 6 路 NMOS Driver

- ✓ 栅极驱动电压从 8V 到 20V

- ✓ 输出级拉电流/灌电流能力 1.5A/1.8A

- ➤ UM32xxx

- ✓ 内置 6 路 PMOS+NMOS Driver

- ✓ 内置 5V/40mA LDO

- ✓ 栅极驱动电压从 5V 到 30V

- ✓ 输出级拉电流/灌电流能力 50mA/300mA

#### ● 主要电气参数

➤ 工作电压: 2.3 ~ 5.5V

▶ 工作温度: -40~+105℃

➤ ESD 防护: ±8kV (HBM)

#### ● 开发支持

- ➤ IAP 应用程序更新

- ▶ JTAG->SWD 模式在线调试/下载功能

- ▶ 完整 SDK 开发包、EVB 硬件开发套件

- ▶ 离线烧录器

# 3 存储器和总线架构

# 3.1 系统架构

#### 主系统由以下部分构成:

- 2个AHB总线Masters:

- ➤ Cortex-M0+

- ➤ DMA控制器

- 5个AHB总线Slaves:

- ➤ FLASH存储器

- ➤ SRAM存储器

- ➤ AHB, AHB to APB Bridge,包含所有APB接口外设和所有AHB接口外设

- ➤ DIV除法器

- ➢ SQRT开方运算器

# 3.2 总线架构图

图 3-1: 总线架构图

# 3.3 存储器映射 (Memory Mapping)

图 3-2: 存储器地址映射图

表 3-1: 存储器和模块地址分配

| 模块名          | 地址分配                     | 大小    |

|--------------|--------------------------|-------|

| EFLASH       | 0x0000_0000——0x0000_8000 | 32 KB |

| EEPROM       | 0x0001_0000——0x0001_1000 | 4 KB  |

| NVR1         | 0x0101_0000——0x0101_0200 | 512 B |

| NVR2         | 0x0101_0200——0x0101_0400 | 512 B |

| NVR3         | 0x0101_0400——0x0101_0600 | 512 B |

| EFC Register | 0x0110_0000——0x0110_006C | 108 B |

| SRAM1        | 0x2000_0000——0x2000_0C00 | 3 KB  |

| SRAM2        | 0x2000_0C00——0x2000_1800 | 3 KB  |

| UART0/1      | 0x4000_0000——0x4000_0400 | 1 KB  |

| SPI          | 0x4000_0800——0x4000_0C00 | 1 KB  |

| GTIMER0      | 0x4000_0C00——0x4000_1000 | 1 KB  |

| LPTIMER      | 0x4000_1000——0x4000_1400 | 1 KB  |

| CRC          | 0x4000_1800——0x4000_1C00 | 1 KB  |

| ADC          | 0x4000_1C00——0x4000_2000 | 1 KB  |

| SYSREG(SCU)  | 0x4000_2000——0x4000_2400 | 1 KB  |

| WDT          | 0x4000_2400——0x4000_2800 | 1 KB  |

| GTIMER1      | 0x4000_3400——0x4000_3800 | 1 KB  |

| GTIMER2      | 0x4000_3800——0x4000_3C00 | 1 KB  |

| WWDT         | 0x4000_3C00——0x4000_4000 | 1 KB  |

| GPIOA        | 0x4000_4000——0x4000_4400 | 1 KB  |

| GPIOB        | 0x4000_4400——0x4000_4800 | 1 KB  |

| GPIOC        | 0x4000_4800——0x4000_4C00 | 1 KB  |

| GPIOD        | 0x4000_4C00——0x4000_5000 | 1 KB  |

| I2C          | 0x4000_5400——0x4000_5800 | 1 KB  |

| ATIMER       | 0x4000_7400——0x4000_7800 | 1 KB  |

| DMAC         | 0x4002_0000——0x4002_0C00 | 3 KB  |

| DIV          | 0x4002_1000——0x4002_1400 | 1 KB  |

| SQRT         | 0x4002_1400——0x4002_1800 | 1 KB  |

UM32Mx56 用户手册 处理器

# 4 处理器

## 4.1 概述

Cortex™ M0+处理器是 32 位的两级流水线 RISC 处理器,内嵌 AMBA-Lite 接口和嵌套向量中断控制器(NVIC)。具有硬件调试功能,可以执行 Thumb 指令,并与其它 Cortex-M 系列兼容。同时加入多项全新设计,改进调试和追踪能力、减少每条指令循环(IPC)数量和改进 Flash 访问的两级流水线等,更纳入了节能降耗技术。Cortex M0+处理器全面支持已整合 Keil & IAR 调试器。

## 4.2 主要特性

- ARMv6 M Thumb

- Thumb/Thumb 2 技术

- ARMv6 M 兼容 24 位 SysTick 定时器

- 32 位硬件乘法器

- 系统接口支持小端 (little-endian) 数据访问

- 准确而及时的中断处理能力

- 加载、存储多个数据和多周期乘法指令可被终止然后重新开始从而实现快速中断处理

- C 应用程序二进制接口的异常兼容模式 (C-ABI); ARMv6 M 的模式允许用户使用纯 C 函数实现中断处理

- 使用中断唤醒(WFI)与事件唤醒(WFE)指令进入低功耗的休眠模式,或从中断退出休眠模式

# 4.3 功能框图

图 4-1: Cortex-M0+处理器功能框图

# 4.4 内核寄存器组

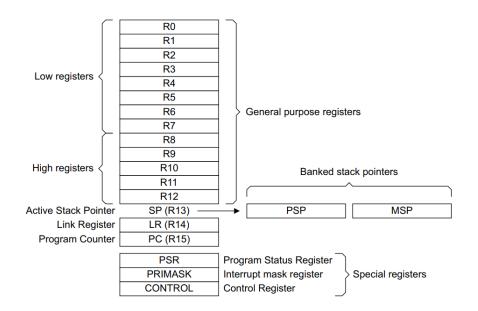

Cortex-M0+处理器寄存器组如下图:

图 4-2: Cortex-M0+的寄存器组

# 5 系统配置 (SCU)

# 5.1 时钟框图

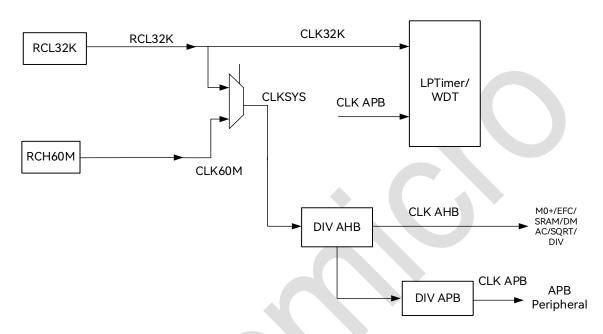

图 5-1: 时钟模块框图

# 5.2 时钟选择

系统存在 2 个时钟源:

- 60MHz 高精度内部时钟 RCH, 作为系统时钟源。

- 32kHz 的内部时钟 RCL,作为低功耗时钟,可作为系统时钟源

根据工作模式不同,采用不同时钟方案,通过配置系统控制寄存器 0(SYSCTRL0)[14]位 CLK\_SEL 来选择系统时钟的来源。关系如下表所示:

| CLK_SEL | 系统时钟来源 |  |

|---------|--------|--|

| 0       | RCH    |  |

| CLK_SEL | 系统时钟来源 |  |

| 1       | RCL    |  |

表 5-1: 系统时钟选择

UM32Mx56 用户手册 系统配置(SCU)

# 5.3 复位源

芯片有多个复位源, 包括 POR 复位、RESETEN 复位、WDT 复位、WWDT 复位、SOFT\_RESETN 复位、模块软件复位、LVD 复位、LOCKUP 复位。具体复位源如下表:

复位源

描述

内部模拟 POR 上电复位

复位所有

LVR 复位

复位除 CPU DEBUG 逻辑外的所有

LOCKUP 复位

LVD 复位

WDT

复位除EFC以外的其它逻辑

WWDT

SOFT\_RESETN

各模块复位

复位对应 IP 模块

表 5-2: 系统复位源

## 5.3.1 内部 POR 上电复位

内部上电复位 POR: 无条件复位整个芯片。

### 5.3.2 LVR 复位

LVR 复位:无条件复位整个芯片。

## 5.3.3 RESETEN 复位

外部复位 RESETEN 复位除 CPU DEBUG 逻辑外的整个芯片。在 RESETEN 复位状态时,芯片可以连接 SWD 接口。RESETEN 管脚在上电完成后默认作为外部复位,可以通过软件关闭外部复位功能。

UM32Mx56 用户手册 系统配置(SCU)

#### 5.3.4 LOCKUP 复位

当系统连续发生两次 HardFault 时,CPU 会进入 LOCKUP 状态,系统会产生 LOCKUP 复位。 LOCKUP 复位除 EFC 以外的其它逻辑。

#### 5.3.5 LVD 复位

LVD 复位除 EFC 以外的其它逻辑。

### 5.3.6 WDT 复位

看门狗定时器复位除 EFC 外的整个用户电路, 缺省为释放状态。

当软件未能有效阻止超时事件时,看门狗定时器复位。该复位仅发生在软件无法正常执行,可能破坏数据时。在 CPU 处于 HALT 状态时,WDT 停止计数,不会产生复位信号。

### 5.3.7 WWDT 复位

复位除 EFC 以外的其它逻辑。

## 5.3.8 SOFT\_RESETN 复位

此复位由系统产生。系统可以通过写软复位重启,但不复位 EFC 控制器和 IO 相关设置。

## 5.3.9 模块复位

模块复位,通过软件复位各数字模块。

# 5.4 低功耗模式

芯片除正常工作模式外, 为了降低芯片的电流消耗, 提供三种低功耗模式: 休眠 (Sleep) 模式、

UM32Mx56 用户手册 系统配置(SCU)

深度休眠 (Deepsleep) 模式、停止 (Stop) 模式。

在休眠模式下, CM0+停止工作, 保留中断处理功能。其它外设等模块时钟和复位可由软件设置。 休眠模式由 CM0+特定指令 WFI / WFE 进入, 唤醒由中断触发。

深度休眠模式是休眠模式的升级,在此模式下,CM0+停止运行,高速时钟停止运行,低功耗功能模块(LPTIMER、WDT)可以运行。深度休眠模式要先设置 CM0+内部的 DEEPSLEEP 寄存器,然后由 CM0+特定指令 WFI / WFE 进入、唤醒由中断触发。

停止模式下,高速时钟和低速时钟均停止运行,系统无任何运行的时钟,一切外围模块均停止运行。上电复位信号有效,IO 状态保持,IO 中断有效,所有寄存器,RAM 和 CPU 数据保存状态时的功耗;停止模式要先设置系统寄存器中 STOPMODE\_SEL 寄存器和 CM0+内部的 DEEPSLEEP 寄存器,然后由 CM0+特定指令 WFI / WFE 进入,唤醒可以通过 GPIO 边沿/电平唤醒或者通过 LPTIMER外部异步脉冲计数产生中断唤醒。

#### 详细的描述如下表:

表 5-3: 低功耗模式

| ### ####  |                    |    |                             |    |                   |

|-----------|--------------------|----|-----------------------------|----|-------------------|

| 模式        | 模式描述               | 进入 | <b>人条件</b>                  | 退  | 出条件               |

|           | LDO Active 供电, CPU | 1. | 根据需要,关闭各外设模块时               | 1. | CM0+检测到中断或事件发     |

| Sleep     | 大部分休眠 (包括          |    | 钟, 仅留下需要监测中断事件的             | 2. | 生。<br>进入中断服务程序清中断 |

| Сісор     | NVIC), WIC 不休眠; 软  |    | 模块。                         |    | 并返回。              |

|           | 件可关闭各模块时钟。         | 2. | 执行 WFI/WFE 指令。              | 3. | 继续执行后续指令。         |

|           | LDO Standby 供电,    | 1. | 根据需要,关闭各外设模块时               | 1. | CM0+检测到中断或事件发     |

|           | CPU 大部分休眠(包括       |    | 钟,仅留下需要监测中断事件的<br>模块。       |    | 生。                |

| DeepSleep | NVIC), WIC 不休眠; 高  | 2. | 候场。<br>设置 CM0+内部的 DeepSleep | 2. | 进入中断服务程序清中断       |

|           | 速时钟源关闭, RCL 低速     |    | 寄存器。                        |    | 并返回。              |

|           | 时钟源运行。<br>         | 3. | 执行 WFI/WFE 指令。              | 3. | 继续执行后续指令。         |

|           |                    | 1. | 根据需要,设置 IO 唤醒的条件。           | 1. | 外部 IO 唤醒事件到来。     |

|           |                    | 2. | 设置 CM0+内部的 DeepSleep        | 2. | CM0+检测到 IO 唤醒事件   |

| Stop      | LDO Standby 供电,关   |    | 寄存器。                        |    | 中断发生。             |

| Осор      | 闭系统所有时钟。           | 3. | 设置系统寄存器中的                   | 3. | 进入中断服务程序清中断       |

|           |                    |    | STOPMODE_SEL 寄存器。           |    | 并返回。              |

|           |                    | 4. | 执行 WFI/WFE 指令。              | 4. | 继续执行后续指令。         |

UM32Mx56 用户手册 系统配置(SCU)

低功耗模式的进入和唤醒条件阐述如下:

Sleep, DeepSleep, Stop 模式进入条件都需要调用 WFI/WFE; 三者模式的唤醒本质是都是需要产生中断或者事件发生。

- Sleep 模式下, 高速时钟 RCH 以及内部低速时钟 RCL 维持进入低功耗模式前的设置, 只要系统产生中断就可以唤醒退出。

- DeepSleep 模式下,RCH 时钟关闭了,RCL 时钟根据设置在工作,所以只有工作在低频时钟源的模块如 WDT、LPTIMER 可以产生中断唤醒退出,以及 GPIO 边沿/电平模式在无时钟情况下产生中断唤醒退出。

- Stop 模式下, 所有时钟源关闭, 可以通过 GPIO 边沿/电平模式在无时钟情况下产生中断唤醒退出, 或者通过 LPTIMER 外部异步脉冲计数产生中断唤醒退出。

#### 5.4.1 Sleep 模式

进入 Sleep 模式设置:

- SCB->SCR 的 bit2 配置为 0

- 调用 WFI/WFE 进入 sleep 模式

唤醒条件:中断唤醒。

#### 5.4.2 DeepSleep 模式

DeepSleep 唤醒源包括: WDT、LPTIMER 中断唤醒,GPIO 边沿/电平中断唤醒。 下面以 PD3 管脚下降沿唤醒为例阐述配置流程:

- 1. 配置外围模块时钟控制寄存器PERI\_CLKEN[19], 使能GPIOD时钟。

- 2. 配置外围模块复位控制寄存器PERI RESET[19], GPIOD设置正常工作。

- 3. 配置端口PD功能寄存器PD\_SEL[15:12],配置PD3为GPIO功能。

- 4. 配置GPIOD数据方向寄存器GPIO\_DIR[3], PD3为输入。

- 5. 配置GPIOD中断触发模式寄存器GPIO IS[3]、PD3边沿触发中断。

UM32Mx56 用户手册 系统配置(SCU)

- 6. 配置GPIOD中断边沿触发设置寄存器GPIO\_IBE[3], PD3单边触发。

- 7. 配置GPIOD中断高低电平触发设置寄存器GPIO\_IEV,下降沿触发。

- 8. 配置GPIOD中断使能寄存器GPIO\_IEN[3],使能PD3中断。

- 9. 配置端口输入配置寄存器PAD IE[27], PD3输入使能。

- 10. 配置端口上拉配置寄存器PAD\_PU[27], PD3上拉使能。

- 11. SCB -> SCR[2]配置为 1。

- 12. 调用 WFI 进入 Deepsleep 模式。

- 13. 中断产生后, 能将系统从深度休眠模式下唤醒。

#### 5.4.3 Stop 模式

Stop 模式唤醒源包括: GPIO 边沿/电平中断唤醒,或者通过 LPTIMER 外部异步脉冲计数产生中断唤醒。

下面以 PD3 管脚下降沿唤醒为例阐述配置流程:

- 1. 配置外围模块时钟控制寄存器PERI\_CLKEN[19],使能GPIOD时钟。

- 2. 配置外围模块复位控制寄存器PERI\_RESET[19], GPIOD设置正常工作。

- 3. 配置端口PD功能寄存器PD\_SEL[15:12],配置PD3为GPIO功能。

- 4. 配置GPIOD数据方向寄存器GPIO DIR[3], PD3为输入。

- 5. 配置GPIOD中断触发模式寄存器GPIO\_IS[3], PD3边沿触发中断。

- 6. 配置GPIOD中断边沿触发设置寄存器GPIO IBE[3], PD3单边触发。

- 7. 配置GPIOD中断高低电平触发设置寄存器GPIO\_IEV,下降沿触发。

- 8. 配置GPIOD中断使能寄存器GPIO IEN[3],使能PD3中断。

- 9. 配置端口输入配置寄存器PAD IE[27]、PD3输入使能。

- 10. 配置端口上拉配置寄存器PAD PU[27]、PD3上拉使能。

- 11. 配置STOPMODE\_SEL = 0xA5A50001; //STOP模式有效。

- 12. SCB -> SCR[2]配置为 1。

13. 调用\_WFI(); //进入STOP模式。

14. 中断产生后,能将系统从Stop模式下唤醒。

#### 5.5 系统寄存器

SYSREG (SCU) 寄存器基地址: 0x4000\_2000

表 5-4: 系统寄存器列表

| 偏置    | 名称              | 描述                               |

|-------|-----------------|----------------------------------|

| 0x000 | SCU_CTRL0       | 系统控制寄存器 0                        |

| 0x008 | SCU_CTRL_PROT   | 系统控制保护寄存器                        |

| 0x00C | SCU_OSC_CTRL    | 时钟控制寄存器                          |

| 0x010 | SCU_PERI_CLKEN  | 外设时钟门控寄存器                        |

| 0x020 | SCU_RESET_FLAG  | 复位标识寄存器                          |

| 0x024 | SCU_PERI_RESET  | 外围模块复位控制寄存器                      |

| 0x028 | SCU_EXTRST_CTRL | 外部复位滤波控制寄存器                      |

| 0x030 | SCU_PA_SEL      | 端口 PA 功能配置寄存器,只能外部复位和 POR 复位此寄存器 |

| 0x034 | SCU_PB_SEL      | 端口 PB 功能配置寄存器,只能外部复位和 POR 复位此寄存器 |

| 0x038 | SCU_PC_SEL      | 端口 PC 功能配置寄存器,只能外部复位和 POR 复位此寄存器 |

| 0x03C | SCU_PD_SEL      | 端口 PD 功能配置寄存器,只能外部复位和 POR 复位此寄存器 |

| 0x054 | SCU_PAD_ADS     | 端口数模配置寄存器,只能外部复位和 POR 复位此寄存器     |

| 0x060 | SCU_PAD_DR      | 端口驱动能力配置寄存器,只能外部复位和 POR 复位此寄存器   |

| 0x06C | SCU_PAD_PU      | 端口上拉配置寄存器,只能外部复位和 POR 复位此寄存器     |

| 0x078 | SCU_PAD_PD      | 端口下拉配置寄存器,只能外部复位和 POR 复位此寄存器     |

| 0x084 | SCU_PAD_OD      | 端口开漏输出配置寄存器,只能外部复位和 POR 复位此寄存器   |

| 0x090 | SCU_PAD_CS      | 端口输入类型配置寄存器,只能外部复位和 POR 复位此寄存器   |

| 0x09C | SCU_PAD_IE      | 端口输入配置寄存器,只能外部复位和 POR 复位此寄存器     |

| 0x0A4 | SCU_PAD_STATUS  | 端口输入电平寄存器                        |

| 0x0A8 | SCU_PAD_SR      | 端口速率配置寄存器,只能外部复位和 POR 复位此寄存器     |

| 0x0B4 | SCU_IOCTRL_PROT | IO 控制保护寄存器                       |

| 0x0B8 | SCU_LVD_CFG     | LVD 控制寄存器                        |

| 0x0BC | SCU_PGA_CFG     | PGA 控制寄存器                        |

| 0x0D0 | SCU_EXTRST_SEL  | 外部复位端口选择寄存器                      |

| 0x0D4 | SCU_STOP_SEL    | 停止模式选择寄存器                        |

| 0x0D8 | SCU_SOFT_RSTN   | 软件复位寄存器                          |

| 0x0DC | SCU_VET_OFFSET  | 中断向量地址重映射寄存器                     |

| 偏置    | 名称           | 描述         |  |  |  |

|-------|--------------|------------|--|--|--|

| 0x0FC | SCU_LVD_INTR | LVD 中断寄存器  |  |  |  |

| 0x188 | SCU_VREF     | VREF 控制寄存器 |  |  |  |

## 5.5.1 系统控制寄存器 0 SCU\_CTRL0 (偏移: 000h)

| 比特    | 名称           | 属性  | 复位值  | 描述                                 |

|-------|--------------|-----|------|------------------------------------|

| 31:29 | RSV          | -   | -    | 保留                                 |

|       |              | DIA | 0.0  | IO 作为时钟输出时,输出时钟选择:                 |

| 20.27 | CLIVOLIT CEL |     |      | 00: HCLK_OUT (系统时钟)                |

| 28:27 | CLKOUT_SEL   | RW  | 0x0  | 01: RCL 时钟                         |

|       |              |     |      | 10/11: PCLK_OUT                    |

| 26:17 | RSV          | -   | _    | 保留                                 |

|       |              |     |      | 连接 ULINK 或者 JLINK 后,在 DEEPSLEEP 或者 |

| 14    | SWD WACK EN  | RW  | 0.41 | STOP 模式下,唤醒系统的使能位:                 |

| 16    | SWD_WACK_EN  | KVV | 0x1  | 1: 在上述条件下,使用 NMI 中断唤醒系统            |

|       |              |     |      | 0: 在上述条件下,不唤醒系统                    |

| 15    | RSV          | -   | -    | 保留                                 |

|       |              |     |      | 系统时钟来源选择:                          |

| 14    | CLK_SEL      | RW  | 0x0  | 0: 高速时钟 CLK_SEL_HF                 |

|       |              |     |      | 1: 低速时钟 CLK_SEL_LF                 |

| 13:11 | RSV          | -   | -    | 保留                                 |

|       |              |     |      | PCLK 分频选择:                         |

|       |              |     |      | 00: HCLK                           |

| 10:9  | PCLK_DIV     | RW  | 0x0  | 01: HCLK/2                         |

|       |              |     |      | 10: HCLK/4                         |

|       |              |     |      | 11: HCLK/8                         |

|       |              |     |      | HCLK 分频选择:                         |

|       |              |     |      | 000: SystemClk                     |

|       |              |     |      | 001: SystemClk/2                   |

|       |              |     |      | 010: SystemClk/4                   |

| 8:6   | HCLK_DIV     | RW  | 0x3  | 011: SystemClk/8                   |

|       |              |     |      | 100: SystemClk/16                  |

|       |              |     |      | 101: SystemClk/32                  |

|       |              |     |      | 110: SystemClk/64                  |

|       |              |     |      | 111: SystemClk/128                 |

| 5:3   | RSV          | -   | _    | 保留                                 |

| 比特 | 名称     | 属性     | 复位值   | 描述                              |

|----|--------|--------|-------|---------------------------------|

|    |        |        |       | 内部低速时钟 RCL 使能控制:                |

| 2  | RCL_EN | RW     | 0x1   | 0: 关闭                           |

|    |        |        | 1: 使能 |                                 |

| 1  | RSV    | -      | -     | 保留                              |

|    |        | RW 0x1 |       | 内部高速时钟 RCH 使能信号:                |

|    | RCH_EN |        | 0x1   | 0: 关闭                           |

| 0  |        |        |       | 1: 使能                           |

|    |        |        |       | 注: 当系统进入 DeepSleep, 此高速时钟会自动关闭。 |

#### 5.5.2 系统控制保护寄存器 SCU\_CTRL\_PROT (偏移: 008h)

| 比特   | 名称              | 属性 | 复位值 | 描述                                                                                                                                                                       |

|------|-----------------|----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:0 | SYSCTRL_PROTECT | RW | 0x0 | 寄存器 SCU_CTRL0 写保护的控制寄存器。给此寄存器写 0xA5A5_5A5A,启动寄存器 SCU_CTRL0 的写使能。给此寄存器写其他值,关闭它们的写使能。SCU_CTRL0 寄存器配置完后,它们的写使能会自动关闭。<br>读此寄存器返回 SCU_CTRL0 寄存器的写使能状态。<br>0: 写未使能<br>1: 写已经使能 |

## 5.5.3 时钟控制寄存器 SCU\_OSC\_CTRL (偏移: 0x00Ch)

| 比特    | 名称         | 属性 | 复位值   | 描述                                                       |

|-------|------------|----|-------|----------------------------------------------------------|

| 31:28 | RSV        | -  | ı     | 保留                                                       |

| 27:16 | WAKP_delay | RW | 0x25A | 系统从 DEEPSLEEP/STOP 模式唤醒,CLK 给出的时间延时。此寄存器的时间为系统时钟计数的时钟周期。 |

| 15:0  | RSV        | -  | -     | 保留                                                       |

#### 5.5.4 外围模块时钟寄存器 SCU\_PERI\_CLKEN (偏移: 010h)

| 比特 | 名称              | 属性   | 复位值         | 描述          |

|----|-----------------|------|-------------|-------------|

| 21 | 31 DIV_CLKEN RW | D\A/ | 00          | DIV 模块时钟使能: |

| 31 |                 | 0x0  | 1: 使能 0: 关闭 |             |

| 比特    | 名称                 | 属性     | 复位值  | 描述                           |

|-------|--------------------|--------|------|------------------------------|

| 30    | UART1_CLKEN        | RW     | 0x0  | UART1 模块时钟使能:                |

| 30    | OARTI_CEREN        | IXVV   | 0.00 | 1: 使能 0: 关闭                  |

| 29:28 | RSV                | -      | -    | 保留                           |

| 27    | ATIMER_CLKEN       | RW     | 0x0  | ATIMER 模块时钟使能:               |

|       | 7.111 IEIX_OEIXEIX | 1000   | OAG  | 1: 使能 0: 关闭                  |

| 26    | SQRT_CLKEN         | RW     | 0x0  | SQRT 模块时钟使能:                 |

|       |                    |        |      | 1: 使能 0: 关闭                  |

| 25    | WWDT_CLKEN         | RW     | 0x0  | WWDT 模块时钟使能:                 |

|       | _                  |        |      | 1: 使能 0: 关闭                  |

| 24:23 | RSV                | -      | -    | 保留                           |

| 22    | DMA_CLKEN          | RW     | 0x0  | DMA 模块时钟使能:                  |

|       |                    |        |      | 1: 使能 0: 关闭                  |

| 21:20 | RSV                | -      | -    | 保留                           |

| 19    | GPIOD_CLKEN        | RW     | 0x0  | GPIOD 模块时钟使能:                |

|       |                    |        |      | 1: 使能 0: 关闭                  |

| 18    | GPIOC_CLKEN        | RW     | 0x0  | GPIOC 模块时钟使能:                |

|       |                    |        |      | 1: 使能 0: 关闭                  |

| 17    | GPIOB_CLKEN        | RW     | 0x0  | GPIOB 模块时钟使能:                |

|       | ^                  |        |      | 1: 使能 0: 关闭                  |

| 16    | GPIOA_CLKEN        | RW     | 0x0  | GPIOA 模块时钟使能:<br>1: 使能 0: 关闭 |

|       |                    |        |      | I2C 模块时钟使能:                  |

| 15    | I2C_CLKEN          | RW     | 0x0  | 120 候块的好使能。<br>  1: 使能 0: 关闭 |

|       |                    |        |      | ADC 控制器模块时钟使能:               |

| 14    | ADC_CLKEN          | RW     | 0x0  | 1: 使能 0: 关闭                  |

| 13    | RSV                |        | _    | 保留                           |

| .0    |                    | · ·    |      | WDT 模块时钟使能:                  |

| 12    | WDT_CLKEN          | RW     | 0x0  | 1: 使能 0: 关闭                  |

|       |                    |        |      | CRC16 模块时钟使能:                |

| 11    | CRC_CLKEN          | RW     | 0x0  | <br>  1: 使能 0: 关闭            |

| 10    | RSV                | _      | _    | 保留                           |

|       | <b></b>            | 5      |      | GTIMERO 模块时钟使能:              |

| 9     | GTIMER0_CLKEN      | RW     | 0x0  | 1: 使能 0: 关闭                  |

|       | L DTIMED CLUES     | D) 4 / | 0.0  | LPTIMER 模块时钟使能:              |

| 8     | LPTIMER_CLKEN      | RW     | 0x0  | 1: 使能 0: 关闭                  |

| 7:5   | RSV                | -      | _    | 保留                           |

| 比特 | 名称                 | 属性  | 复位值   | 描述               |

|----|--------------------|-----|-------|------------------|

| 4  | SPI CLKEN          | RW  | 0x0   | SPI 模块时钟使能:      |

| 4  | SPI_CLKEN          | KVV | UXU   | 1: 使能 0: 关闭      |

| 2  | CTIMED2 CLIVEN     | DW  | 0.0   | GTIMER 2 模块时钟使能: |

| 3  | 3 GTIMER2_CLKEN RW | KVV | W 0x0 | 1: 使能 0: 关闭      |

|    | CTIMED1 CLIVEN     | DW  | 0.40  | GTIMER 1 模块时钟使能: |

| 2  | GTIMER1_CLKEN      | RW  | 0x0   | 1: 使能 0: 关闭      |

| 1  | RSV                | -   | -     | 保留               |

|    | 0 UARTO_CLKEN RW   | DW  | 0x0   | UARTO 模块时钟使能:    |

| U  |                    | KVV |       | 1: 使能 0: 关闭      |

## 5.5.5 复位标识寄存器 SCU\_RESET\_FLAG(偏移: 020h)

| 比特   | 名称               | 属性  | 复位值 | 描述                           |

|------|------------------|-----|-----|------------------------------|

| 31:8 | RSV              | -   | -   | 保留                           |

|      |                  |     |     | CPU 复位状态,需要软件初始化和清除。         |

|      |                  |     |     | 1: Cortex M0+系统复位发生          |

| 7    | SYS_RSTREQ_FLAG  | W1C | 0x0 | 0: 无复位发生                     |

|      |                  |     |     | 此位只能被 PORN 和外部 RESETN 复位,写 1 |

|      |                  |     |     | 清 0。                         |

|      |                  |     |     | CPU 死锁复位状态,需要软件初始化和清除。       |

|      |                  |     |     | 1: Lockup 复位发生               |

| 6    | LOCKUP_RSTN_FLAG | W1C | 0x0 | 0: 无复位发生                     |

|      |                  |     |     | 此位只能被 PORN 和外部 RESETN 复位,写 1 |

|      |                  |     |     | 清 0。                         |

|      |                  |     |     | 低电压复位状态,需要软件初始化和清除。          |

|      |                  |     |     | 1: LVD 复位发生                  |

| 5    | LVD_RSTN_FLAG    | W1C | 0x0 | 0: 无复位发生                     |

|      |                  |     |     | 此位只能被 PORN 和外部 RESETN 复位,写 1 |

|      |                  |     |     | 清 0。                         |

|      |                  |     |     | 窗口看门狗复位状态,需要软件初始化和清除。        |

|      |                  |     |     | 1: WWDT 复位发生                 |

| 4    | WWDT_FLAG        | W1C | 0x0 | 0: 无复位发生                     |

|      |                  |     |     | 此位只能被 PORN 和外部 RESETN 复位,写 1 |

|      |                  |     |     | 清 0。                         |

| 比特 | 名称          | 属性  | 复位值 | 描述                           |

|----|-------------|-----|-----|------------------------------|

|    |             |     |     | 看门狗复位状态,需要软件初始化和清除。          |

|    |             |     |     | 1: WDT 复位发生                  |

| 3  | WDT_FLAG    | W1C | 0x0 | 0: 无复位发生                     |

|    |             |     |     | 此位只能被 PORN 和外部 RESETN 复位,写 1 |

|    |             |     |     | 清 0。                         |

|    | RESETN_FLAG | W1C | 0x0 | 外部复位状态,需要软件初始化和清除。           |

| 2  |             |     |     | 1: 外部复位发生                    |

| 2  |             |     |     | 0: 无复位发生                     |

|    |             |     |     | 此位只能被 PORN 复位,写 1 清 0。       |

|    |             | W1C | 0x0 | Soft 复位状态,需要软件初始化和清除。        |

|    |             |     |     | 1: Soft 复位发生                 |

| 1  | SOFTR_FLAG  |     |     | 0: 无复位发生                     |

|    |             |     |     | 此位只能被 PORN 和外部 RESETN 复位,写 1 |

|    |             |     |     | 清 0。                         |

| 0  | RSV         | -   | _   | 保留                           |

注:复位标识寄存器只能被 PORN 复位。

## 5.5.6 外围模块复位控制寄存器 SCU\_PERI\_RESET (偏移: 024h)

| 比特    | 名称                 | 属性   | 复位值 | 描述                  |

|-------|--------------------|------|-----|---------------------|

| 31    | 31 DIV RESET       | RW   | 0x0 | DIV 模块复位使能:         |

| 31    | DIV_RESET          | KVV  | UXU | 1: 正常工作 0: 模块处于复位状态 |

| 30    | UART1_RESET        | RW   | 0x0 | UART1 模块复位使能:       |

| 30    | OARTI_RESET        | KVV  | UXU | 1: 正常工作 0: 模块处于复位状态 |

| 29:28 | RSV                | _    | _   | 保留                  |

| 27    | 27 ATIMER_RESET RV | D)A/ | 0.0 | ATIMER 模块复位使能:      |

| 21    |                    | RVV  | 0x0 | 1: 正常工作 0: 模块处于复位状态 |

| 26    | CODT DECET         | RW   | 0x0 | SQRT 模块复位使能:        |

| 20    | SQRT_RESET         | RVV  |     | 1: 正常工作 0: 模块处于复位状态 |

| 25    | WWDT RESET         | RW   | 0.0 | WWDT 模块复位使能:        |

| 25    | WWWDI_RESET        | KVV  | 0x0 | 1: 正常工作 0: 模块处于复位状态 |

| 24:23 | RSV                | -    | -   | 保留                  |

| 22    | DMA DECET          | DIA  | 0.0 | DMA 控制器模块复位使能:      |

| 22    | DMA_RESET          | RW   | 0x0 | 1: 正常工作 0: 模块处于复位状态 |

| 比特    | 名称               | 属性   | 复位值  | 描述                  |

|-------|------------------|------|------|---------------------|

| 21:20 | RSV              | -    | -    | 保留                  |

| 19    | CDIOD DECET      | RW   | 0x0  | GPIOD 模块复位使能:       |

| 19    | GPIOD_RESET      | RVV  | UXU  | 1: 正常工作 0: 模块处于复位状态 |

| 18    | GPIOC_RESET      | RW   | 0x0  | GPIOC 模块复位使能:       |

| 10    | GPIOC_RESET      | KVV  | UXU  | 1: 正常工作 0: 模块处于复位状态 |

| 17    | GPIOB_RESET      | RW   | 0x0  | GPIOB 模块复位使能:       |

| 17    | GFIOD_RESET      | KVV  | UXU  | 1: 正常工作 0: 模块处于复位状态 |

| 16    | GPIOA_RESET      | RW   | 0x0  | GPIOA 模块复位使能:       |

| 10    | OFTOA_INESET     | IXVV | 0.00 | 1: 正常工作 0: 模块处于复位状态 |

| 15    | I2C_RESET        | RW   | 0x0  | I2C 模块复位使能:         |

| 13    | IZC_INESET       | IXVV | 0.00 | 1: 正常工作 0: 模块处于复位状态 |

| 14    | ADC_RESET        | RW   | 0x0  | ADC 控制器模块复位使能:      |

| 14    | ADC_RESET        | IXVV | UXU  | 1: 正常工作 0: 模块处于复位状态 |

| 13    | RSV              | -    | _    | 保留                  |

| 12    | WDT_RESET        | RW   | 0x0  | WDT 模块复位使能:         |

| 12    | WDI_RESET        | IXVV | UXU  | 1: 正常工作 0: 模块处于复位状态 |